## **Report**

# Impact of Lowering the HBM-IC-Robustness on the Automotive-System-Level-Robustness

to **ESD Forum e.V.**

19<sup>th</sup> September 2011

Dipl.-Ing. Friedrich zur Nieden Dipl.-Ing. Stanislav Scheier Prof. Dr.-Ing. Stephan Frei

Arbeitsgebiet Bordsysteme

Technische Universität Dortmund

Friedrich-Wöhler-Weg 4

D-44227 Dortmund

# **Contents**

| In | troduction. |                                                         | 5  |

|----|-------------|---------------------------------------------------------|----|

| 1  | Demons      | strator PCB and PCBs for IC characterization            | 7  |

|    |             | D demonstrator PCB                                      |    |

|    | 1.1.1       | Voltage regulator                                       | 9  |

|    | 1.1.2       | Coupling between parallel PCB traces                    | 10 |

|    | 1.1.3       | μC                                                      | 11 |

|    | 1.1.4       | LIN transceivers                                        | 13 |

|    | 1.1.5       | CAN transceivers                                        | 14 |

|    | 1.2 TLF     | P-testboards for µC, LIN- and CAN-transceivers          | 15 |

| 2  | Modelin     | g of components                                         | 17 |

|    | 2.1 Pul     | se generators                                           | 17 |

|    | 2.1.1       | HBM model                                               | 17 |

|    | 2.1.2       | Basic IEC generator model                               | 19 |

|    | 2.1.3       | IEC NoiseKen model                                      | 20 |

|    | 2.1.4       | TLP model                                               | 22 |

|    | 2.2 PC      | B trace model (multi conductor transmission line model) | 23 |

|    | 2.3 Mo      | deling of IC structures                                 | 27 |

|    | 2.3.1       | General modeling approach for electrical domain         | 28 |

|    | 2.3.2       | Thermal failure model                                   | 31 |

|    | 2.3.3       | Scaling of the IC ESD robustness                        | 34 |

| 3  | Charact     | erization of selected devices                           | 36 |

|    | 3.1 Sel     | ected ESD protection devices                            | 36 |

|    | 3.2 Cha     | aracterization of selected IC pins with TLP             | 42 |

|    | 3.2.1       | Time domain measurement setup                           | 43 |

|    | 3.2.2       | Frequency domain measurement setup                      | 45 |

|    | 3.2.3       | Characterization of LIN transceiver ATA6662C TxD pin    | 46 |

|    | 3.2.4       | Characterization of CAN transceiver TJA1041T CANH pin   | 51 |

|    | 3.2.5       | Characterization of µC XC864 DATA pin                   | 55 |

|    | 3.3 ICs     | with lower ESD robustness                               | 60 |

|    | 3.3.1       | IEC robustness factor 0,5                               | 60 |

|    | 3.3.2       | HBM robustness factor 0,5                               | 61 |

|    | 3.3.3       | HBM 2 kV and 1 kV robustness                            | 61 |

|    | 3.3.4       | Comparison of scaling Results                           | 62 |

| 4 | M   | leasure     | ement results                                                      | 64   |

|---|-----|-------------|--------------------------------------------------------------------|------|

|   | 4.1 | Cou         | upling between striplines in frequency domain                      | . 64 |

|   | 4.  | 1.1         | Setup                                                              | . 64 |

|   |     | 1.2<br>odel | Comparison with simulation and verification of the transmission 66 | line |

|   | 4.2 | Mea         | asurement of cross-talk signals in time domain                     | . 68 |

|   | 4.  | 2.1         | IEC ESD Generator                                                  | . 68 |

|   | 4.  | 2.2         | TLP                                                                | . 72 |

|   | 4.3 | Imp         | act of protection elements on currents                             | . 77 |

|   | 4.  | .3.1        | Setup                                                              | . 78 |

|   | 4.  | 3.2         | Measurement results                                                | . 78 |

|   | 4.4 | Mea         | asurement of IEC robustness on demonstrator PCB                    | . 85 |

|   | 4.  | 4.1         | Setup                                                              | . 85 |

|   | 4.  | 4.2         | LIN TxD                                                            | . 87 |

|   | 4.  | 4.3         | CANH                                                               | . 90 |

|   | 4.  | 4.4         | μC DATA                                                            | . 92 |

|   | 4.  | 4.5         | Measurement results with protection elements                       | . 94 |

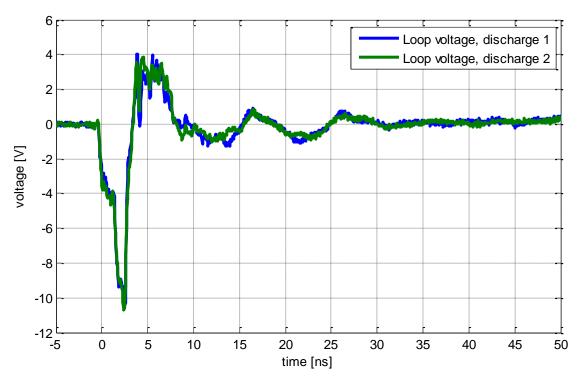

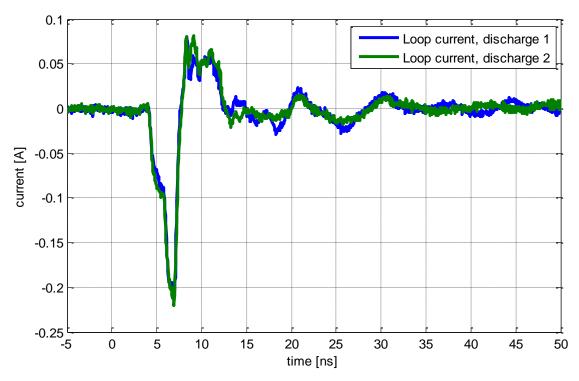

|   | 4.5 | Mea         | asurement of loop voltage and current                              | . 95 |

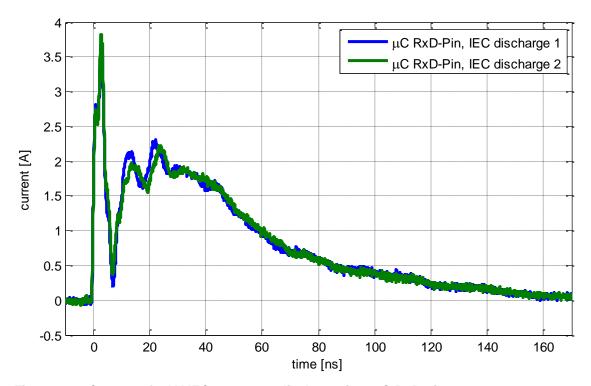

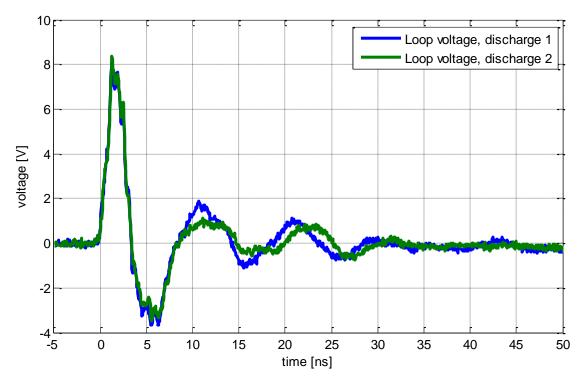

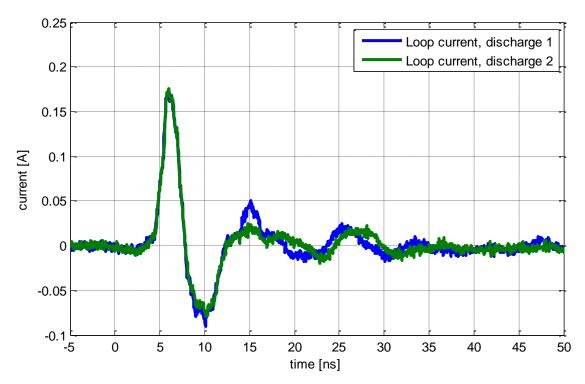

|   | 4.  | 5.1         | Setup                                                              | . 96 |

|   | 4.  | 5.2         | Measurement results                                                | . 96 |

| 5 | S   | imulati     | on results                                                         | 103  |

|   | 5.1 | Sim         | ulation of coupled signals for different load conditions           | 103  |

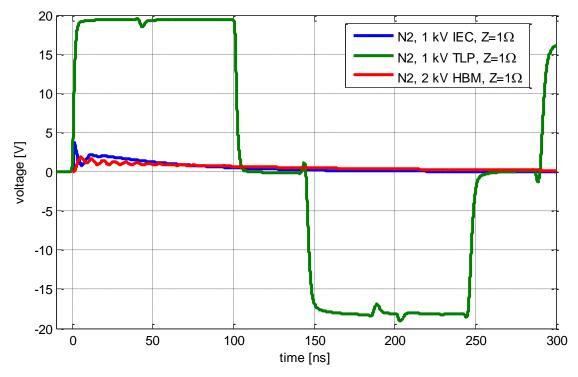

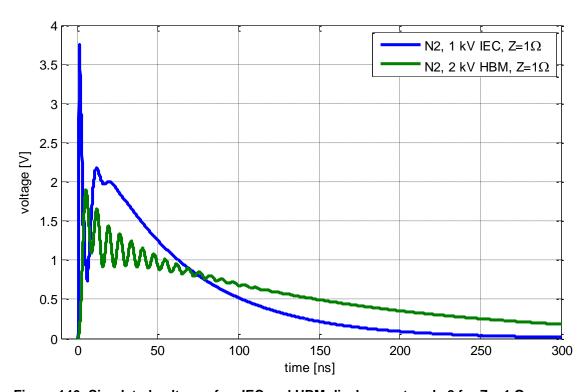

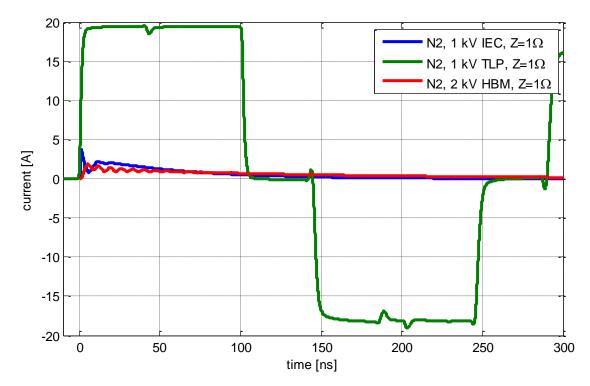

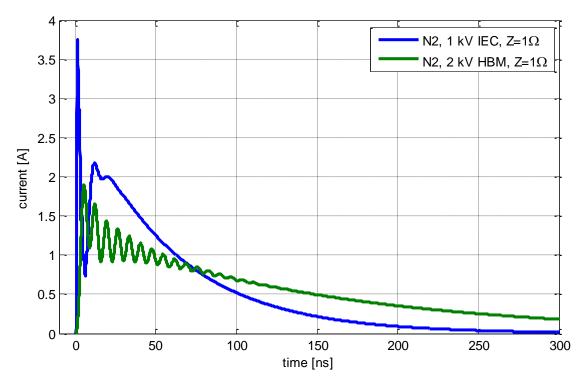

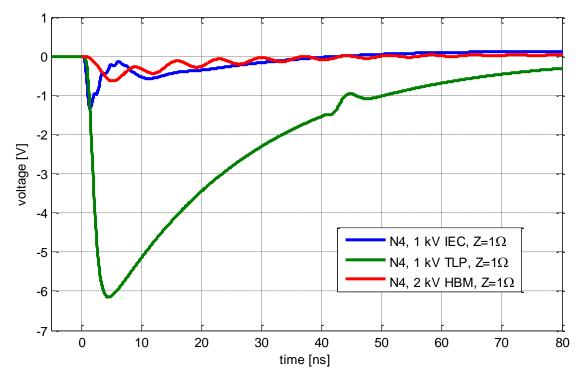

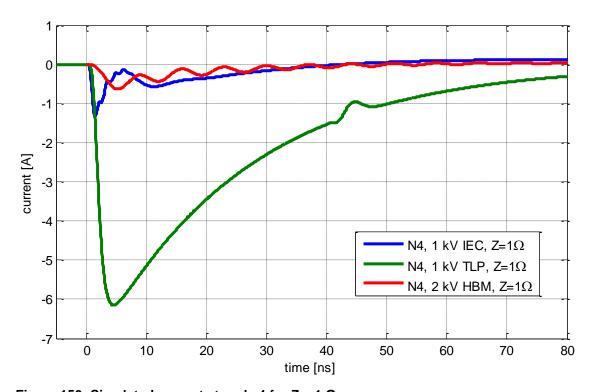

|   | 5.  | 1.1         | Simulated waveforms for $Z = 1 \Omega$                             | 105  |

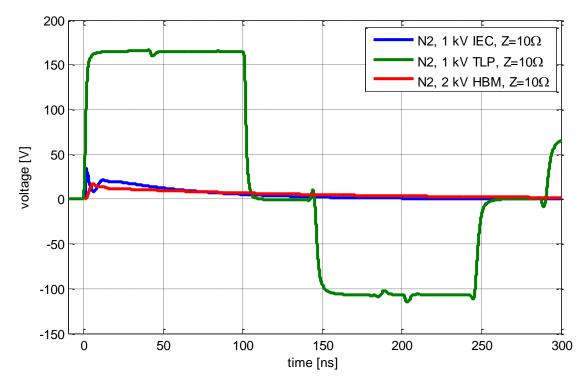

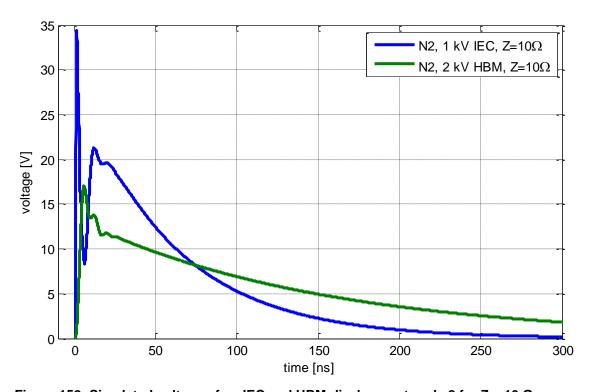

|   | 5.  | 1.2         | Simulated waveforms for $Z = 10 \Omega$                            | 108  |

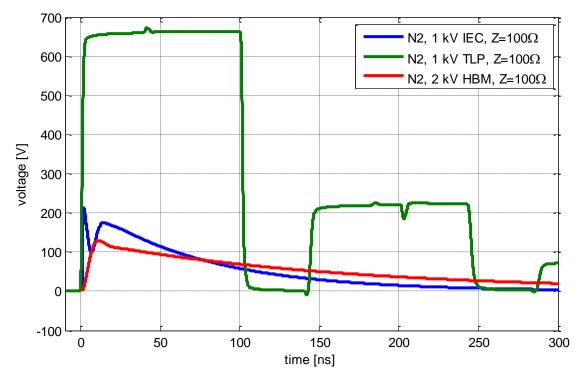

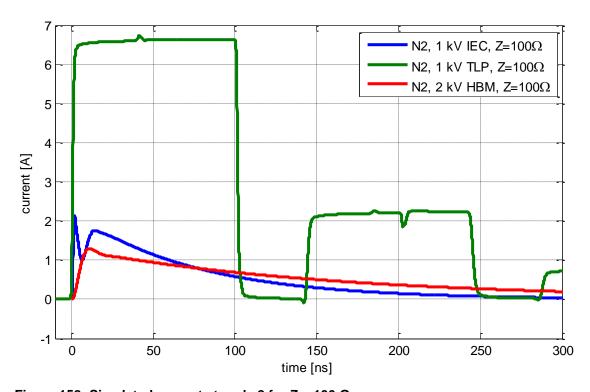

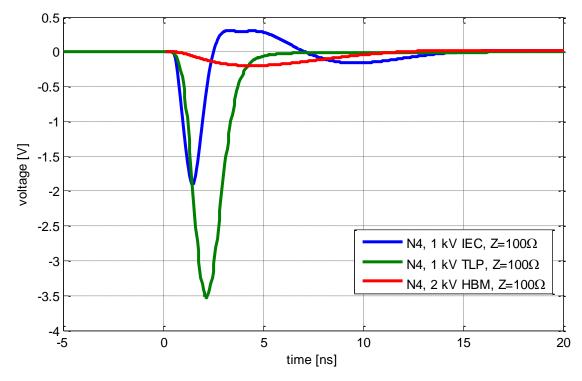

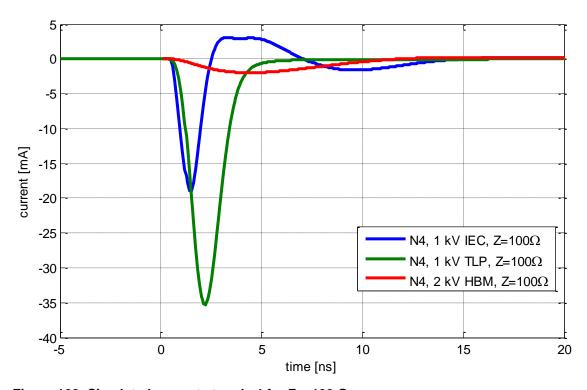

|   | 5.  | 1.3         | Simulated waveforms for $Z = 100 \Omega$                           | 111  |

|   | 5.  | 1.4         | Simulated waveforms for $Z = 1 k\Omega$                            | 113  |

|   | 5.  | 1.5         | Simulated waveforms for Z = 10 $k\Omega$                           | 115  |

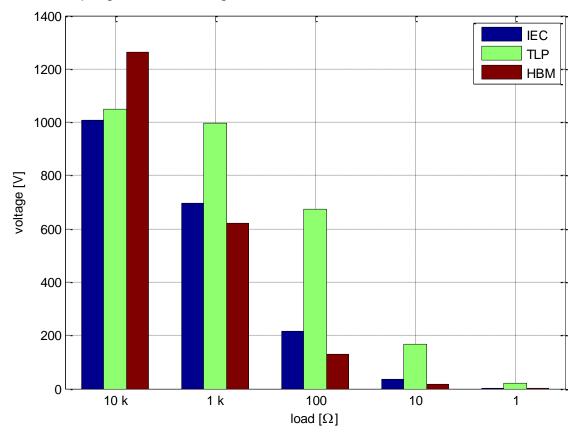

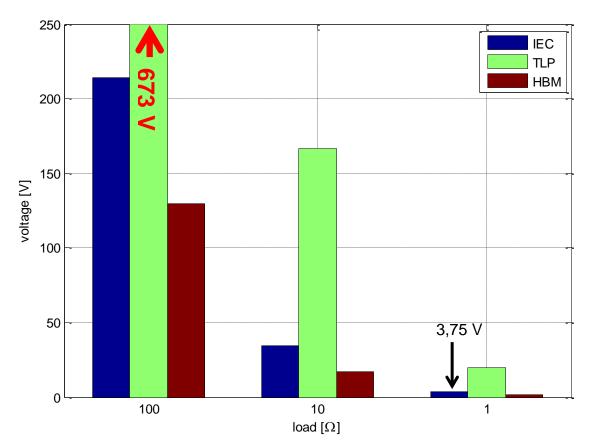

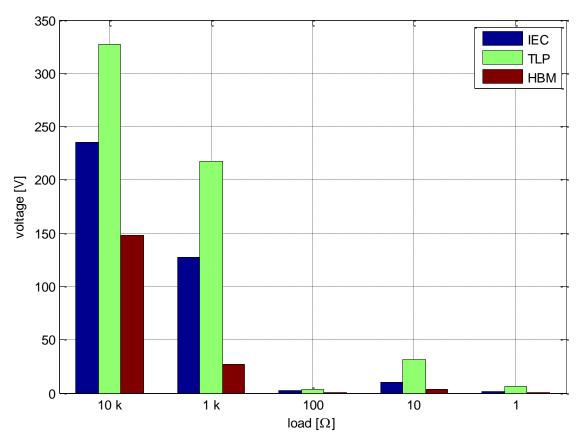

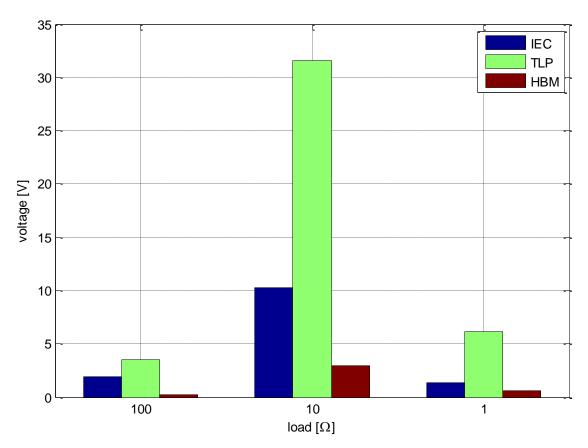

|   | 5.  | 1.6         | Comparison of simulated maximum voltage amplitudes                 | 117  |

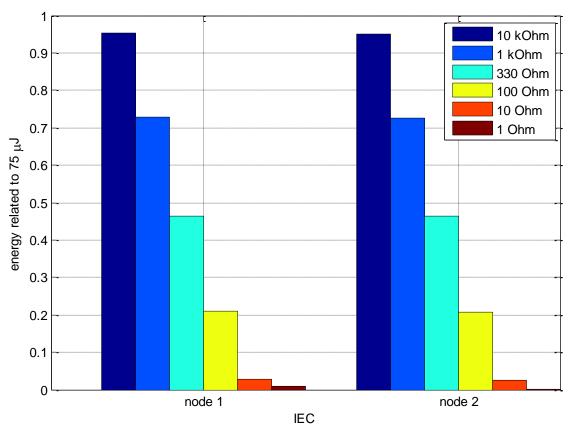

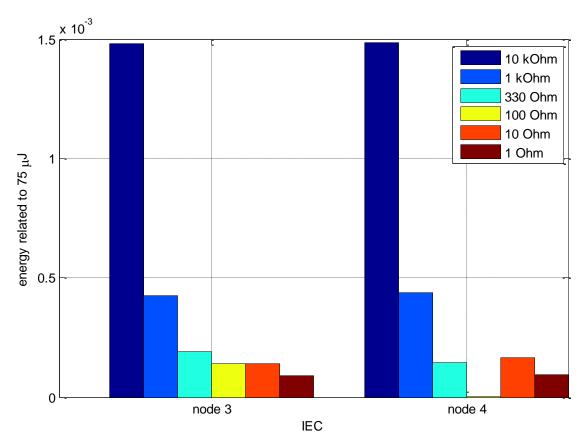

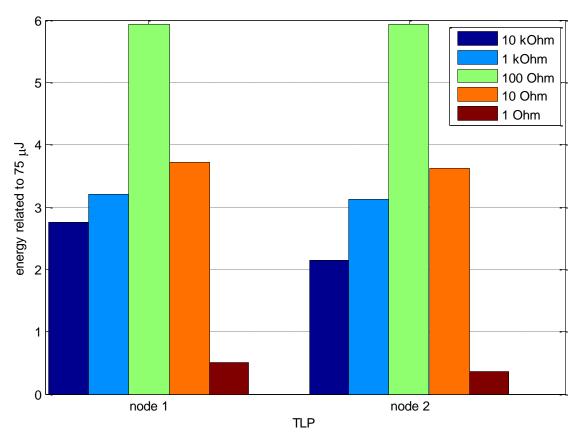

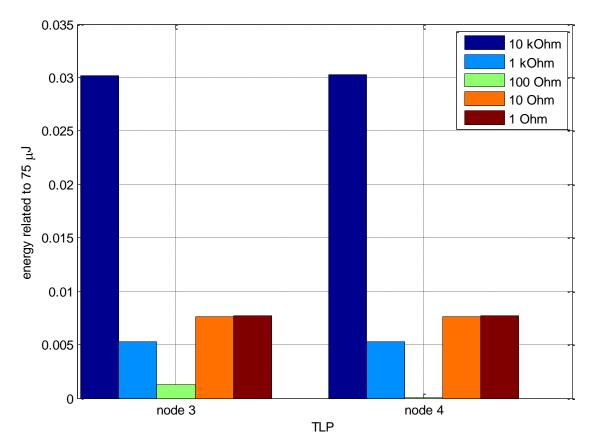

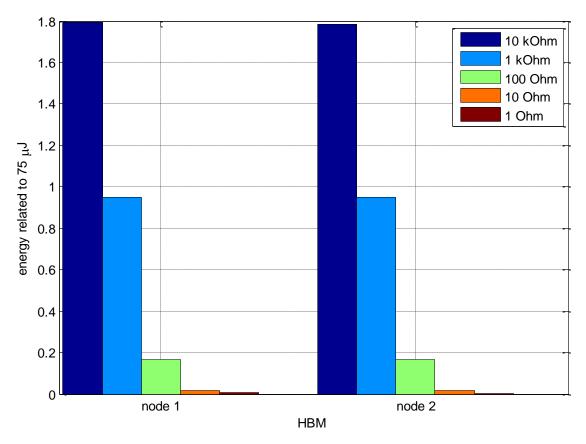

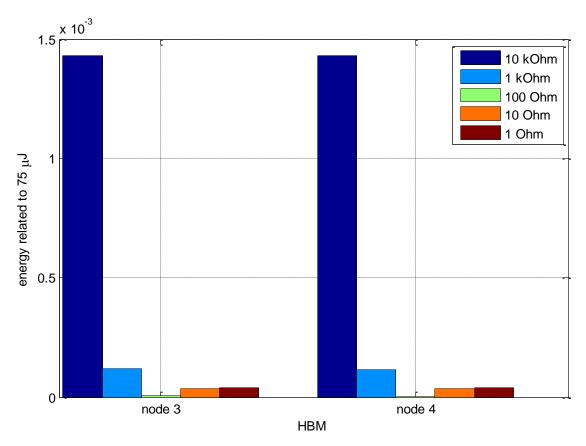

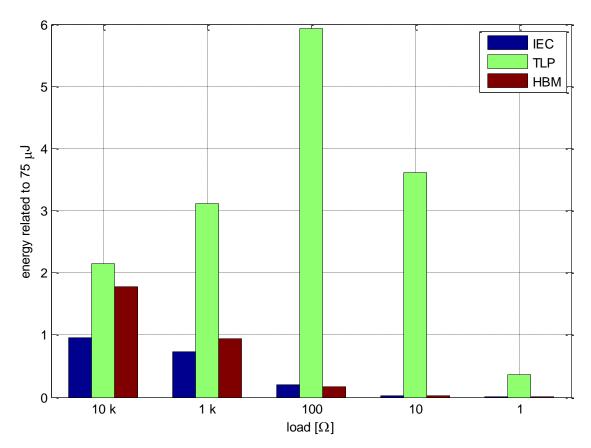

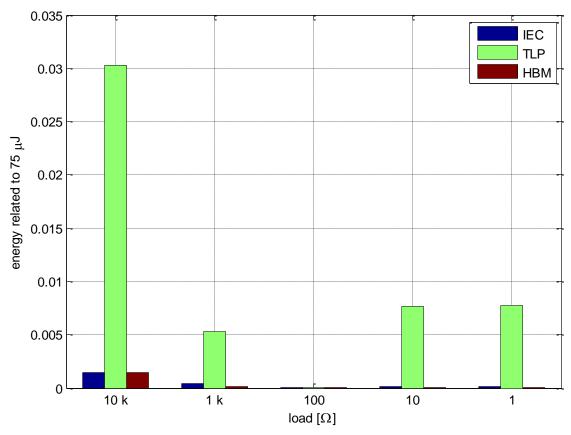

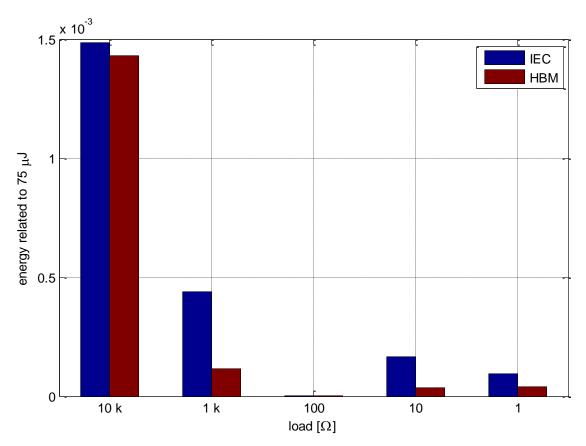

|   | 5.  | 1.7         | Comparison of energy coupled by the different generators           | 119  |

|   | 5.2 | Imp         | act of charging voltage on coupled signals                         | 126  |

|   | 5.  | 2.1         | PCB traces terminated with resistors                               | 126  |

|   | 5.  | 2.2         | Transmission lines terminated with IC IV-characteristics           | 130  |

|   | 5.3 | Effe        | ect of ESD protection elements on coupling signals                 | 133  |

|   | 5.  | 3.1         | 50 $\Omega$ termination with protection element on PCB trace 2     | 133  |

|   | 5.4 | PCI         | B traces terminated with ICs and one protection element on trace 1 | 136  |

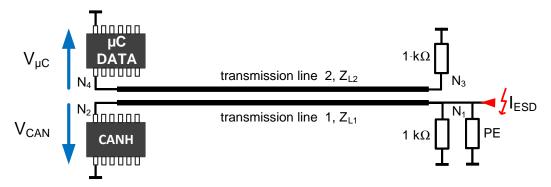

| 5.4.1 |            | 1.1    | Simulation setup                                           | 137 |

|-------|------------|--------|------------------------------------------------------------|-----|

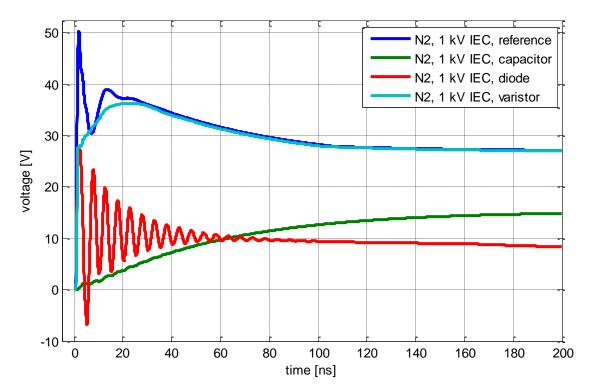

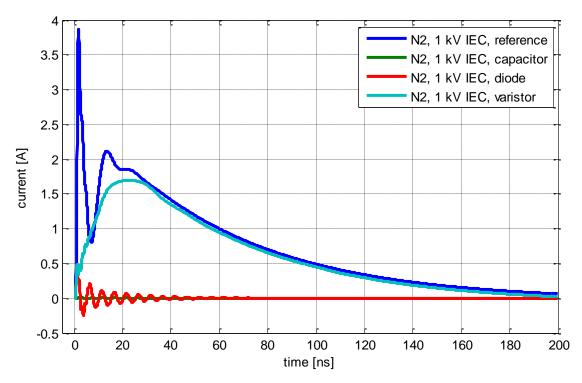

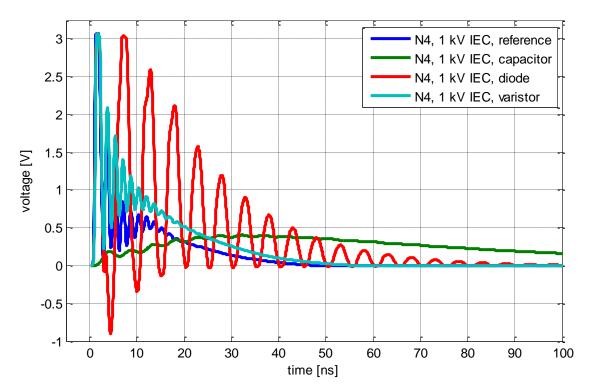

|       | 5.4        | 1.2    | Simulation results                                         | 137 |

|       | 5.5        | PCE    | B traces terminated with ICs and protection elements       | 143 |

|       | 5.5        | 5.1    | Simulation setup                                           | 143 |

|       | 5.5        | 5.2    | Simulation results                                         | 144 |

|       | 5.6        | PCE    | B trace 2 terminated with ESD protection element           | 149 |

|       | 5.6        | 6.1    | Simulation setup                                           | 149 |

|       | 5.6        | 5.2    | Simulation results                                         | 150 |

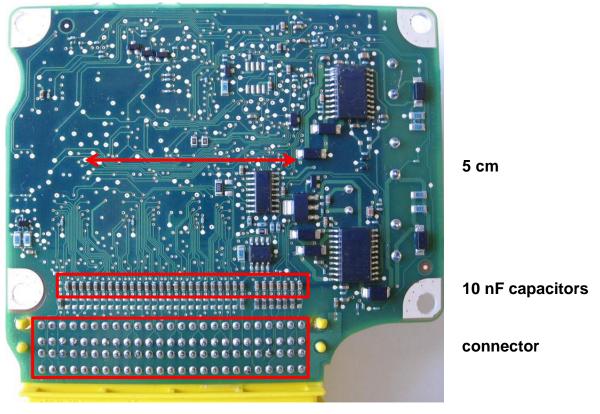

|       | 5.7        | Sim    | ulation with different PCB traces parameter sets           | 153 |

|       | 5.8        | Criti  | ical case simulation                                       | 160 |

|       | 5.8        | 3.1    | 10 nF connected to trace 2                                 | 160 |

|       | 5.8        | 3.2    | 10 nF connected to trace 2 and 220 pF at IC pin at trace 1 | 160 |

|       | 5.8        | 3.3    | Changed IC position                                        | 163 |

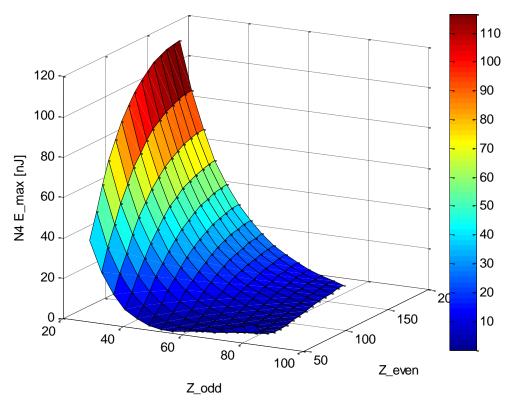

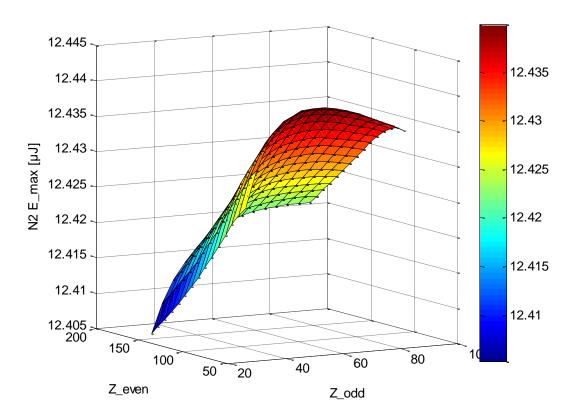

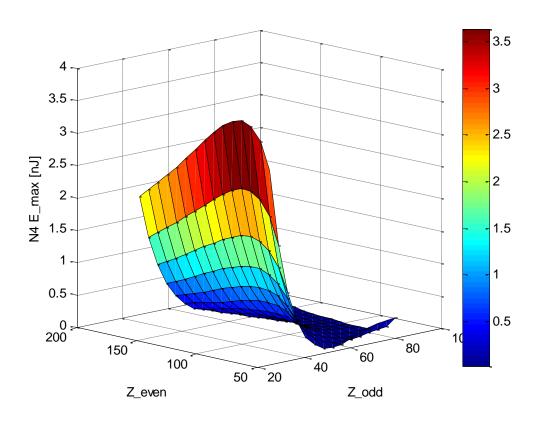

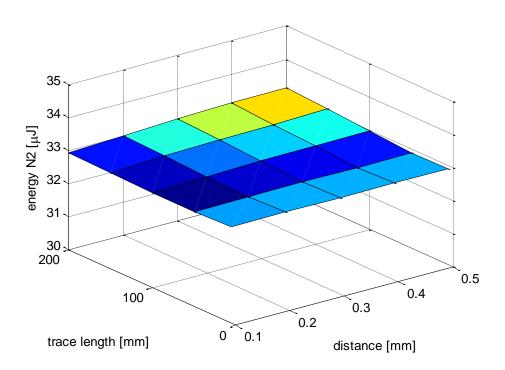

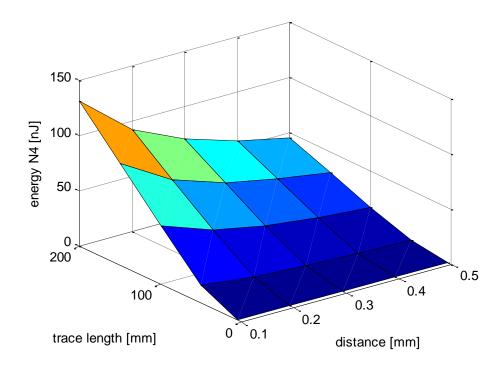

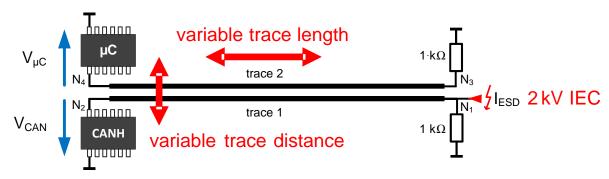

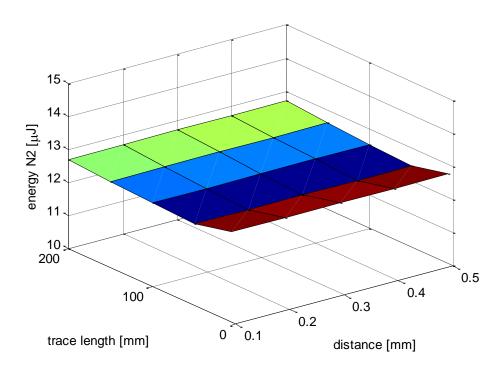

|       | 5.9        | Imp    | act of PCB traces and trace length on IC ESD robustness    | 164 |

| 6     | De         | sign r | rules                                                      | 166 |

| 7     | Summary    |        |                                                            | 169 |

| 8     | References |        |                                                            |     |

## Introduction

The impact of a lower HBM-IC-robustness on the ESD-robustness of automotive systems is currently discussed in industry. In a whitepaper an industry council of semiconductor manufacturers proposes the lowering of component level HBM / MM ESD specifications to save costs [1]. The proposal is based on the following considerations:

- Sufficient protection for packaging and handling is provided by 1 kV HBM testing

- Statistics show that there is no impact of different IC HBM-ESD robustness levels on the ESD failure rates

- Only new ICs applied to circuits without direct connection to automotive electronic control unit connectors would be affected

- Function levels of ICs remain the same but the ESD-robustness is lowered

As a reaction to the proposal the DKE working group AK 767.13.5 proposes detailed investigation on the topics due to the following reasons [2]:

- A lowering of the IC robustness might affect the systems' ESD robustness in case of coupled ESD between global<sup>1</sup> and local pins

- Critical pulse energies at IC pins caused by ESD coupling from connector pins depend on the PCB layout

- If the OEM ESD specifications remain the same, how does a lowering of HBM levels affect the IEC testing?

- What effects can be observed with cable discharge events at connector pins?

- Is there any effect on the choice of external ESD protection elements?

The main objectives of the investigation are based on the questions discussed among members of the automotive industry concerning the publications by the industry council:

- Estimation of the impact of ICs with lower robustness on automotive systems

- Quantification of the disturbances by on-PCB cross-talk

- Quantification of the disturbances through connected cables

- Specification of external ESD protection strategies for compliance with Packaging and Handling demands

<sup>&</sup>lt;sup>1</sup> IC pins can be separated in local and global pins. Global pins can be connected to the ECU connector and might be threatened directly by ESD currents. Local pins have no direct connection to the ECU connector.

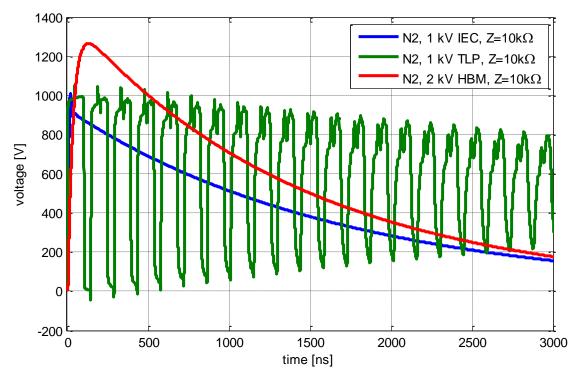

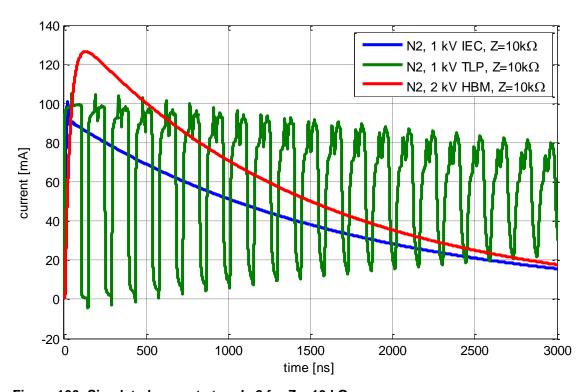

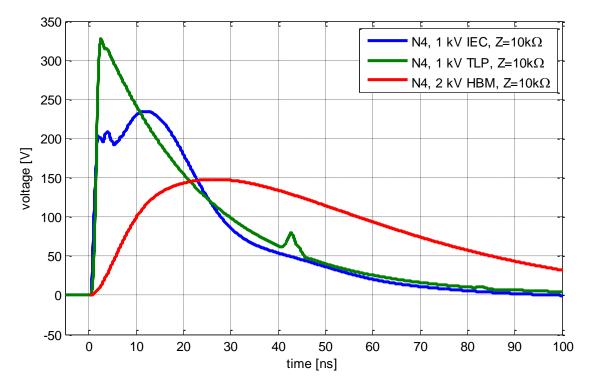

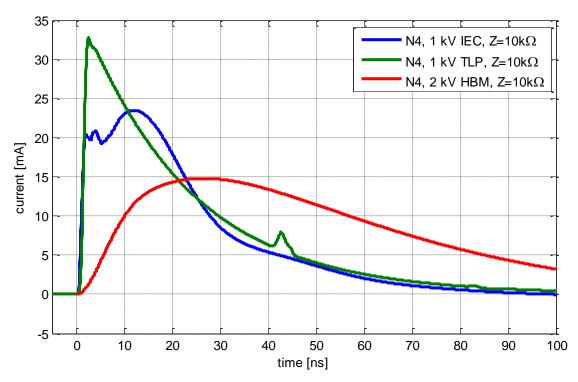

The research work is based mainly on measurements and simulations. All simulations methods are verified by measurements. A demonstrator PCB was developed considering typical automotive electronic configurations. Different test pulses were applied to investigate coupling effects between transmission lines and estimate the disturbance potential for ICs. Common automotive ICs were used as realistic victims ( $\mu$ C, LIN, CAN) and failure levels with direct or field coupled currents were identified by measurement. In this context the effectiveness of external ESD protection elements has been lined out. Another special aspect dealt with the possible disturbance by trace loops on PCBs. Simple loop configurations were considered in the design of the demonstrator.

As a second step models of all components on the demonstrator PCB and in the environment are provided. Transmission line models are used to describe on-PCB traces and cables. The models of conductors were verified by measurement. Coupling of multi conductor transmission line models was verified using 3D simulation.

$\mu$ C, LIN and CAN pins, which are selected as victims for ESD pulses on the demonstrator, are characterized and failure models were developed. The required characteristic datasets were measured using special developed PCBs for the application of TLP (transmission line pulser).

Models of different testing devices like HBM- and IEC generators were applied to investigate the discussed questions. The interconnection of all component models allowed the simulation of maximum coupled amplitudes and energies on IC and connector pins.

The impact of different HBM failure levels on the robustness of automotive electronic control units has been considered by a modification of the parameters of the IC ESD failure models.

## 1 Demonstrator PCB and PCBs for IC characterization

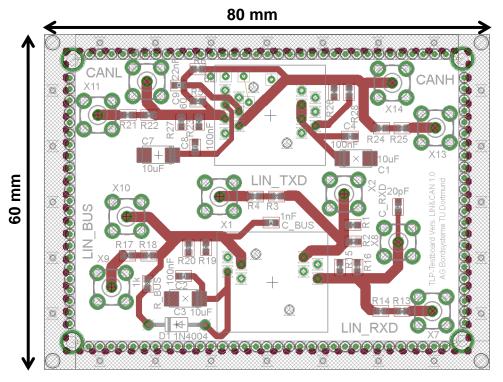

The objectives defined in introduction are investigated by simulation and measurement. For measurement a testboard was designed considering critical PCB-trace configurations. Different types of automotive IC pins can be selected as terminations. The testboard concept, considering LIN-, CAN-transceivers and an 8-bit  $\mu$ C, is described in detail in section 1.1.

In order to create IC failure models, different characteristic datasets of each IC pin have to be measured with a TLP setup for modeling. To ensure a high level of accuracy two special PCBs were designed. The layout for LIN and CAN-transceivers is shown in section 1.2. Selected pins of an 8-bit  $\mu$ C are characterized using the second board described in the same section.

All PCBs are designed double-sided and were manufactured on FR4 material (thickness: 1.55 mm). The thickness of the copper traces is 35 µm.

#### 1.1 ESD demonstrator PCB

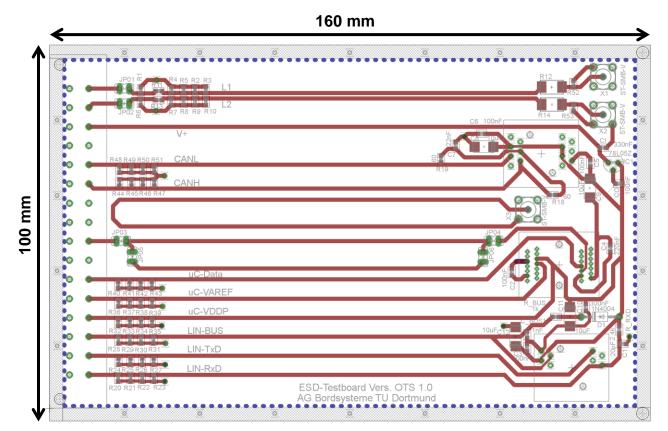

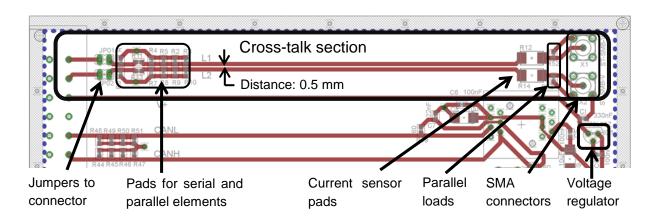

The demonstrator PCB is designed to investigate the disturbance of automotive systems by on-PCB coupling effects caused by ESD. As a second item the potential failure of ICs with lower ESD robustness is analyzed. The allover layout is shown in Figure 1. It can be divided into 4 main sections:

- Voltage regulator

- Cross-talk section with long parallel traces

- Section for investigations with μC (XC-864)

- Section for investigations with LIN transceivers

- Section for investigations with CAN transceivers

Figure 1: ESD demonstrator PCB layout

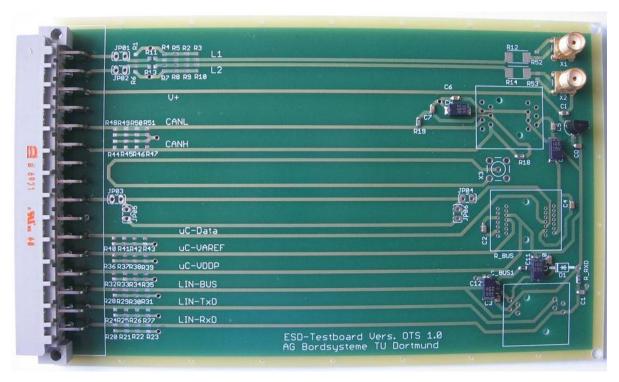

Figure 2: ESD demonstrator PCB with connector

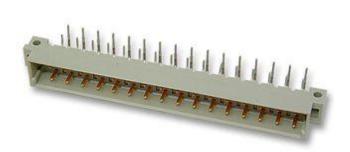

Figure 3: Connector of demonstrator

A 2-row "Harting 09 04 132 6921" connector with 32 pins was chosen for the demonstrator. It is similar to typical automotive connectors. The allover width is 88.9 mm. The connector is suitable for a 5.08 mm grid.

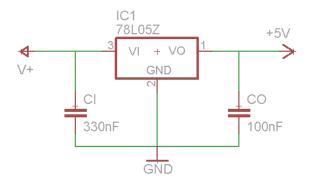

#### 1.1.1 Voltage regulator

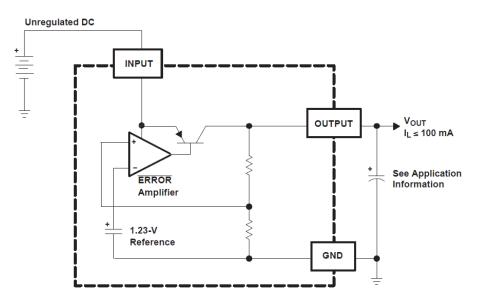

A "Texas Instruments LP2950" voltage regulator was considered in the layout to provide a 5 V supply to the ICs, if powered tests are required. The functional block diagram is shown in Figure 4. Basic characteristics of the element are listed below:

- Wide input voltage range: up to 30 V

- Stable with low ESR (>12 mΩ) capacitors

- Rated output current of 100 mA

- Current- and thermal-limiting features

- Low dropout: 380 mV (typ.) at 100 mA

- Low quiescent current: 75 μA (typ.)

Figure 4: Functional block diagram of voltage regulator

In the layout the voltage regulator is connected to a 330 nF and 100 nF capacitor on the input and output pins (Figure 5). Larger blocking capacitors are not used as influence on ESD pulse propagation is low.

Figure 5: Circuit of voltage regulator

#### 1.1.2 Coupling between parallel PCB traces

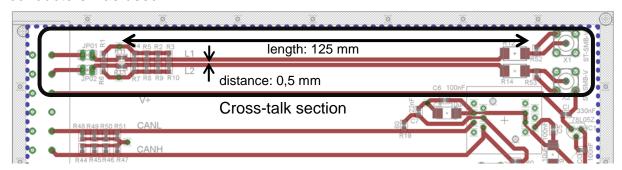

Basic coupling effects can be investigated by two parallel PCB traces. The layout of the coupling (cross-talk) section is shown in Figure 6. A charged structure can be discharged into the upper conductor and the coupled signal can be measured on the lower conductor. Two traces of 1 mm width are placed in 0.5 mm distance to each other. Each trace can be terminated by several serial and parallel elements at both ends. Jumpers allow including the connector in the setup if additional loads or wires should be connected or the influence of the connector should be part of the investigation. The signals on both lines can be measured with an oscilloscope via SMA-connectors or by using small current sensors like Tektronix CT1 or CT6.

Figure 6: Cross-talk section of demonstrator

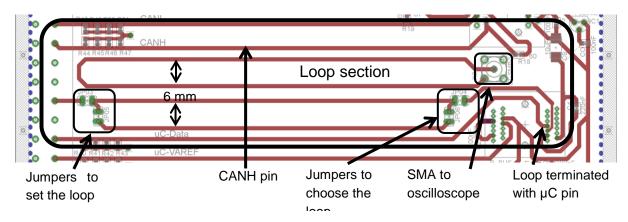

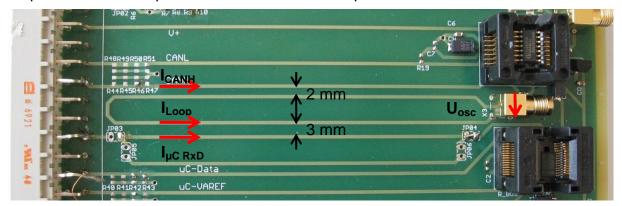

Field coupling on PCBs can occur if conducting loops are part of a design. On the demonstrator board two loops were designed to investigate the potential disturbance of ICs by this effect. If a network is discharged into a conductor close to the loop the induced current can be measured via a SMA connector with an oscilloscope. A

second loop configuration can be chosen with jumpers. The discharge current can be impressed into the connector pin and the loop trace can be terminated with an IC pin.

Figure 7: Coupling into loops

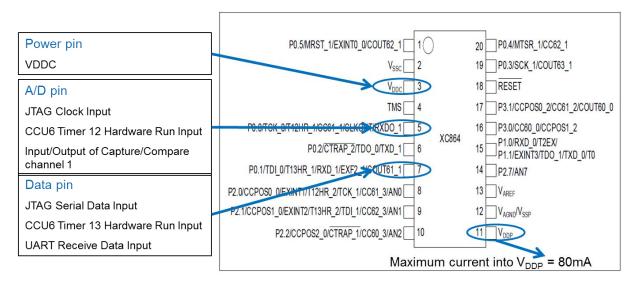

#### 1.1.3 **µC**

The main functionality of automotive electronic control units (ECU) is implemented with programmable microcontrollers. The complex ICs contain different types of elementary circuits. To increase the variety of test options on the demonstrator board several pins of an Infineon 8-bit XC864  $\mu$ C are considered in the layout. The ESD robustness according to the datasheet is specified up to a testing level of 2 kV HBM for all pins.

| IC       | Pins     | ESD protection level              |  |  |

|----------|----------|-----------------------------------|--|--|

| Infineon | All pins | HBM -2kV2kV C=100pF R=1,5 kOhm    |  |  |

| XC864    |          | CDM -500V .500V C=330pF R=150 Ohm |  |  |

| 8-bit μC |          | ·                                 |  |  |

| TSSOP-20 |          |                                   |  |  |

Table 1: ESD protection levels of µC pins as specified in datasheet

Two multipurpose I/O pins and two supply pins ("I/O port supply", "core supply monitor") were selected for testing. The configuration is shown in Figure 8. Although the ESD specification is similar for all pins, a different behavior is expected during characterization and testing.

Figure 8: Selected pins of µC for investigation on demonstrator PCB

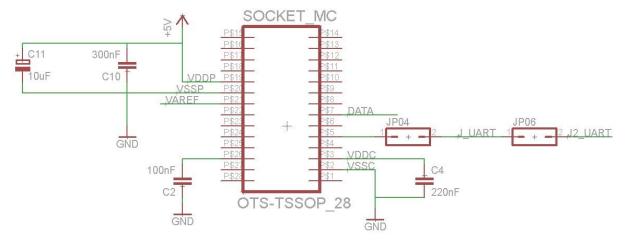

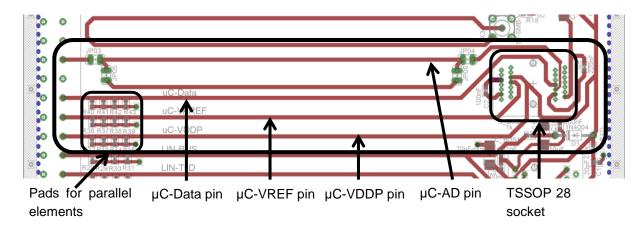

In the circuit diagram in Figure 9 all connections to the  $\mu$ C-IC are drawn. A 10  $\mu$ F and a 300 nF capacitor are connected at VDDP pin. 100 nF are connected to reset input and 220 nF are soldered between VDDC and supply ground pins.

The layout of the demonstrator in the  $\mu C$  section is shown in Figure 10. Because of a better availability a TSSOP28 socket is used in the design so that 8 pins of the socket are left open on the IC side. The data pin, VREF pin, VDDP pin and AD pin are connected to the connector and can be tested with different testing devices. In case of VDDP, VAREF and Data input ESD protection elements can be added parallel to ground.

Figure 9: Circuit connected to µC on demonstrator

Figure 10: µC section on demonstrator PCB

#### 1.1.4 LIN transceivers

Three different LIN transceivers were selected for testing. In comparison to microcontrollers a higher level of ESD protection is specified for most pins. Available parameters from Datasheet are listed in Table 2.

| IC                       | Pins                                | ESD protection level                         |  |

|--------------------------|-------------------------------------|----------------------------------------------|--|

| Infineon<br>TLE7259-2GE  | Bus Pins                            | IEC -11kV11kV C=150pF R=330 Ohm IEC61000-4-2 |  |

| LIN Transceiver PG-DSO-8 | Vs, Bus, WK<br>vs. GND              | HBM -6kV6kV C=100pF R=1,5 kOhm               |  |

|                          | All pins                            | HBM -2kV2kV C=100pF R=1,5 kOhm               |  |

| Atmel<br>ATA6662C        | Vs, LIN vs.<br>GND                  | IEC -6kV6kV C=150pF R=330 Ohm IEC61000-4-2   |  |

| LIN Transceiver SO8      | WK                                  | IEC -5kV5kV C=150pF R=330 Ohm IEC61000-4-2   |  |

|                          | Vs, LIN, WK,<br>INH Pins vs.<br>GND | HBM -6kV6kV C=100pF R=1,5 kOhm               |  |

|                          | All other                           | HBM -3kV3kV C=100pF R=1,5 kOhm               |  |

|                          | Pins                                | MM -100V100V C=500pF R=10 Ohm<br>L=0.75μH    |  |

|                          |                                     | CDM -750V750V C=330pF R=150 Ohm              |  |

Table 2: ESD specifications of selected LIN transceivers

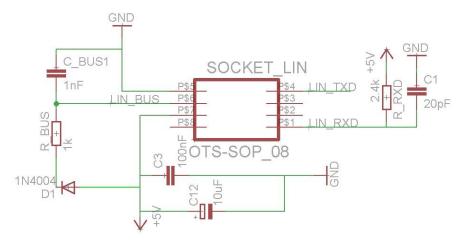

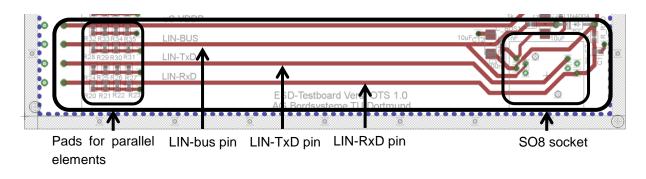

The LIN-bus, LIN-RxD and LIN-TxD pin are connected to the connector on the demonstrator board. For protection parallel elements can be soldered in the current path of each pin. ESD-tests should be done with 100 nF capacitors at LIN-RxD and LIN-Bus pins. The circuit and layout section for LIN transceivers is shown in Figure 11 and Figure 12.

Figure 11: Circuit for LIN transceivers on demonstrator PCB

Figure 12: LIN section on demonstrator PCB

#### 1.1.5 CAN transceivers

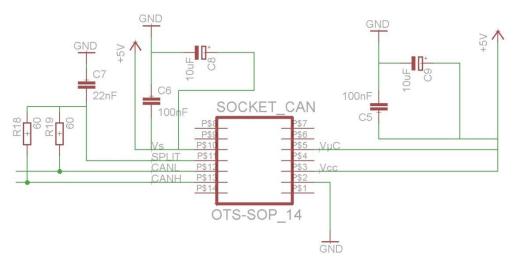

Similar to LIN transceivers often CAN transceivers are part of automotive electronic control units. The selected ICs are designed to withstand minimum 6 kV IEC discharge for global pins. According to Table 3 local pins are specified with 2 kV HBM except the SPLIT-pin of the TLE 6251 G transceiver. The layout is shown in Figure 14. The CANH- and CANL-pins are connected to the demonstrator connector and can be tested in different configurations with optional parallel elements. For ESD testing SPLIT termination and 100 nF at  $V_{cc}$ ,  $V_{\mu C}$  and  $V_s$  pins can be also considered as can be seen in the circuit diagram in Figure 13.

| IC                   | Pins                   | <b>ESD</b> protection level |                     |

|----------------------|------------------------|-----------------------------|---------------------|

| Infineon TLE         | CANH, CANL             | IEC -6 kV6 kV               | C=150 pF R=330 Ohm  |

| 6251 G               |                        | IEC61000-4-2                |                     |

| HS-CAN               | CANH, CANL,            | HBM -6 kV6 kV               | C=100 pF R=1,5 kOhm |

| Transceiver          | WK                     |                             |                     |

| P-DSO-14-13          | SPLIT                  | HBM -1 kV1 kV               | C=100 pF R=1,5 kOhm |

|                      | All other pins         | HBM -2 kV2 kV               | C=100 pF R=1,5 kOhm |

| NXP TJA1041T<br>SO14 | CANH, CANL,<br>SPLIT   | HBM -6 kV6 kV               | C=100 pF R=1,5 kOhm |

|                      | TXD, RXD,<br>VI/O, STB | HBM -3 kV3 kV               | C=100 pF R=1,5 kOhm |

|                      | All other pins         | HBM -4 kV4 kV               | C=100 pF R=1,5 kOhm |

|                      | All pins               | MM -200 V200 V              | C=200 pF R=10 Ohm   |

Table 3: ESD specifications of selected CAN transceivers

Figure 13: Circuit for CAN transceivers on demonstrator PCB

Figure 14: CAN section on demonstrator PCB

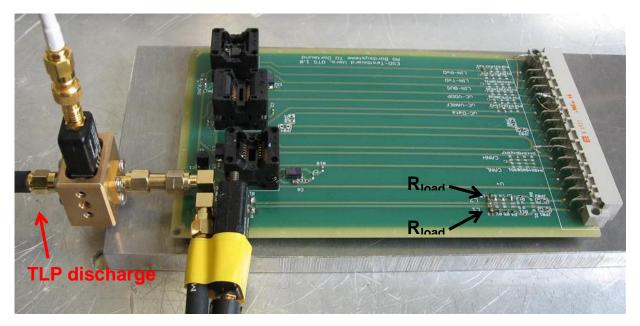

# 1.2 TLP-testboards for $\mu$ C, LIN- and CAN-transceivers

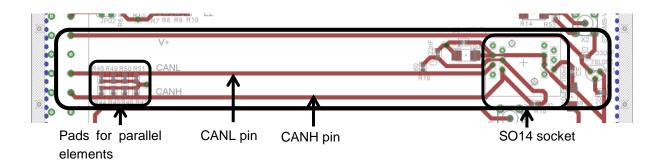

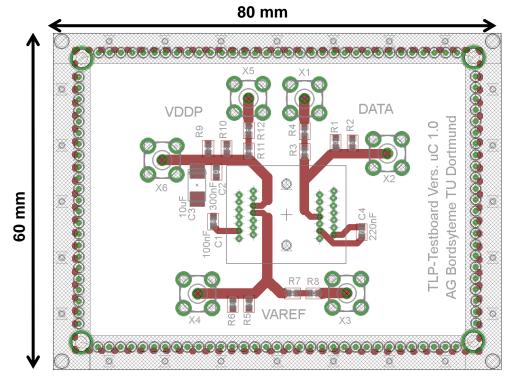

The impact of ICs with lower ESD robustness is partly investigated by simulation techniques. A detailed TLP (transmission line pulser) characterization of all selected

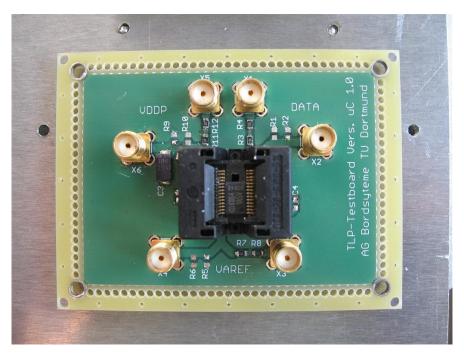

IC pins is required for modeling. For measurement with the TLP the ICs are placed on special testboards. The layout is optimized for short lengths of PCB traces. To prevent reflections due to mismatch, traces are designed to have a line impedance of 50  $\,\Omega$  in order to match to the 50  $\,\Omega$  source impedance of the TLP. The PCBs with dimensions 60 mm x 80 mm are shown in Figure 15 and Figure 16.

Figure 15: TLP testboard with sockets for LIN and CAN transceivers

Figure 16: TLP testboard with µC socket

Capacitors of 10  $\mu$ F can be soldered parallel to the voltage supply pins of all ICs for characterization. Similar wiring and circuits as described for the demonstrator PCB are considered in the TLP PCB layout to make sure that testing conditions are comparable in each setup. As a second testing option the ESD robustness of single IC pins protected by parallel devices can be measured with the TLP setup.

# 2 Modeling of components

In section 2 modeling techniques and already available and during this project created models for the simulation of the ESD pulse propagation on PCBs are described.

## 2.1 Pulse generators

Different standardized pulse generators are used to specify the ESD robustness of electronic systems on component and system level. The models of HBM, IEC and TLP pulse generators are described in the following sections.

#### 2.1.1 **HBM model**

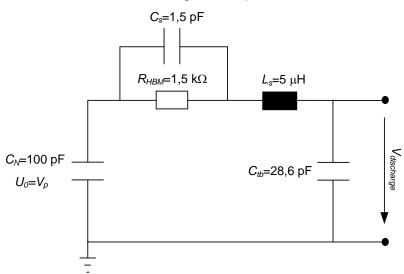

The Human Body Model (HBM) is traditionally used for basic ESD-characterization of integrated circuits. The waveform is defined e.g. in the non-automotive JEDEC JESD22-A114F standard [3]. In [4] a proposal for a HBM generator model is described. The equivalent circuit is shown in Figure 17. Differing from the literature approach the inductor  $L_s$  has been changed to 5  $\mu$ H.

Figure 17: General equivalent circuit of basic HBM generator model

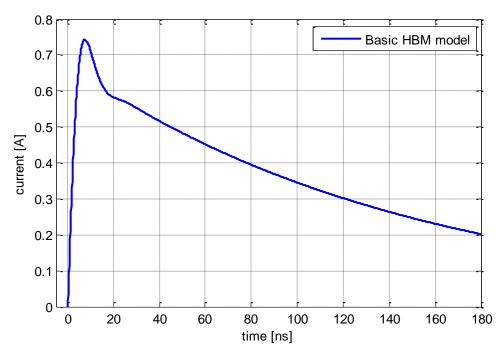

For waveform verification the currents flowing through a 500  $\Omega$  resistor and shorted circuit is measured. The simulated discharge of the HBM model through a 1  $\Omega$  resistor is shown in Figure 18.

Figure 18: Discharge of basic HBM generator model with 1  $\Omega$  load and 1 kV charging voltage

For verification with the short circuit load a pulse rise time of 2-10 ns and peak amplitude of 0,6 to 0,74 A is required if the capacitor is charged with 1000 V.

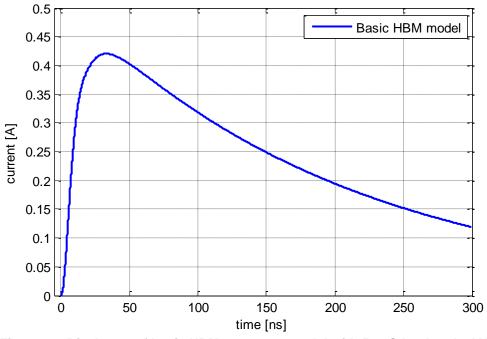

According to the standard a rise time of 5-25 ns and peak current amplitude of 0,37 to 0,55 A has to be measured for the same charging voltage if the generator is connected to 500  $\Omega$ . The simulated waveform is shown in Figure 19.

Figure 19: Discharge of basic HBM generator model with 500  $\Omega$  load and 1 kV charging voltage

#### 2.1.2 Basic IEC generator model

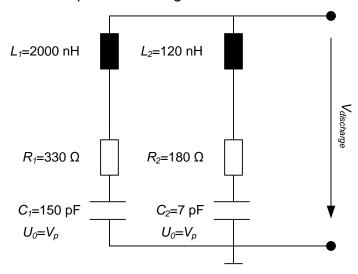

As a general approach the current waveform which is specified in to the standard IEC 61000-4-2 can be simulated by two parallel R, L, C circuits with charged capacitors. The general equivalent circuit is shown in Figure 20. Here the standardized network elements of the ESD-generator are represented by  $R_1$  and  $C_1$ . The inductor  $L_1$  is considered to be the obligatory ground strap with the length of about 2 m.

Physically the first peak of the pulse is shaped by additional lumped and parasitic elements around and in the tip of the ESD-generator.

Figure 20: General equivalent circuit of basic ESD-generator model

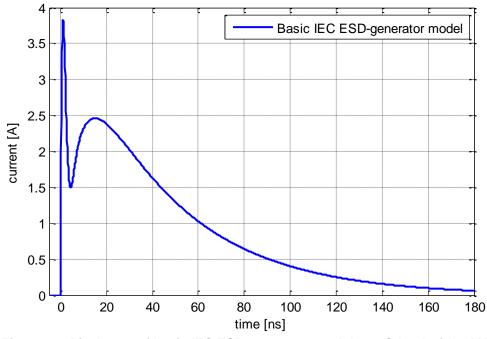

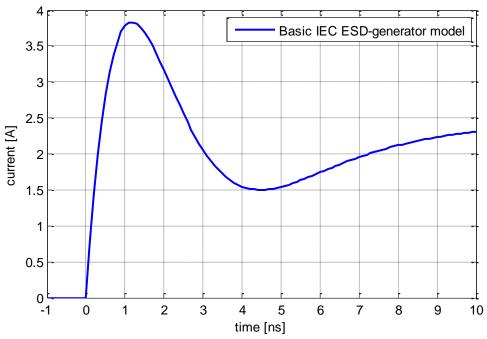

According to the IEC 61000-4-2 standard the current waveform has to be verified with a low ohmic current sensor. The resulting current shape is shown in Figure 21. The first peak and accurate rise-time can be seen in detail in Figure 22.

Figure 21: Discharge of basic IEC ESD-generator model at 2  $\Omega$  load with 1 kV charging voltage

Figure 22: First peak current of basic IEC ESD-generator model at 2  $\Omega$  load with 1 kV charging voltage

#### 2.1.3 IEC NoiseKen model

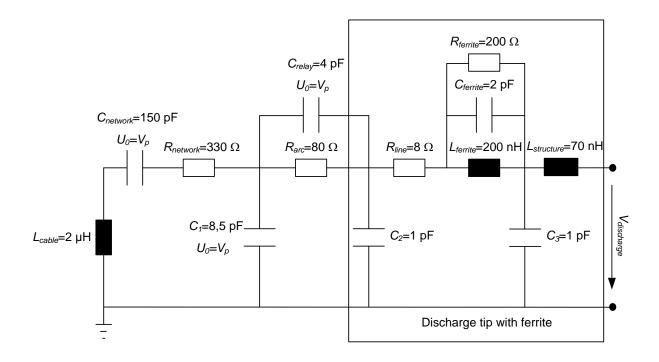

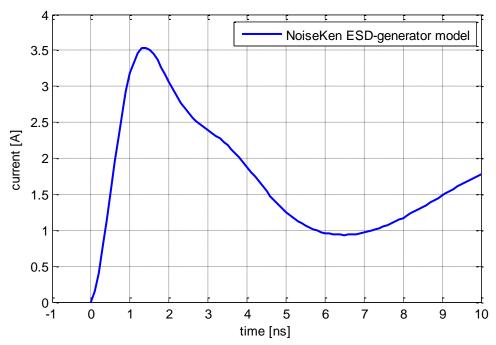

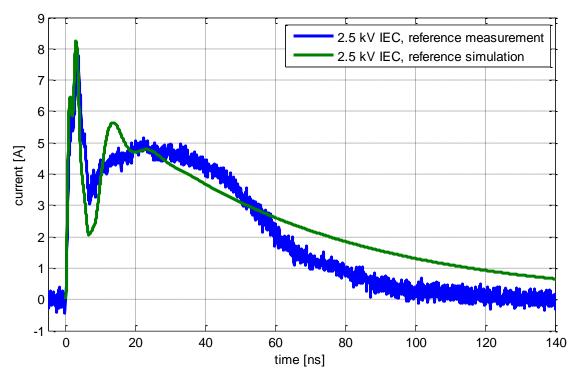

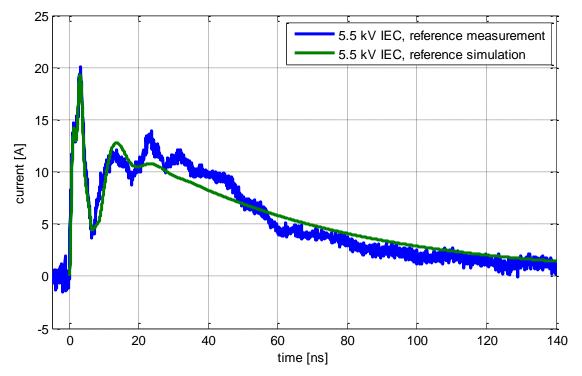

An advanced circuit simulating the discharge of a NoiseKen IEC generator is given in Figure 23. The model has been verified by measurement on different low and high-ohmic loads. More detailed information can be found in [5] and [6].

Figure 23: General equivalent circuit of NoiseKen ESD-generator

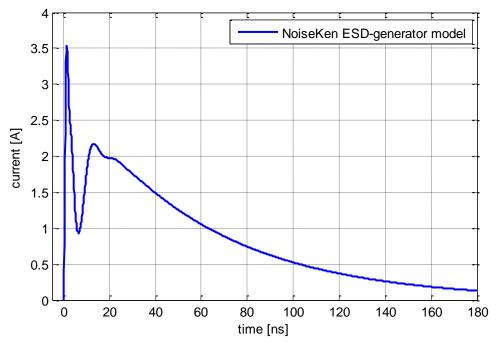

The resulting current shape is shown in Figure 24. The first peak and accurate rise-time can be seen in detail in Figure 25.

Figure 24: Discharge of NoiseKen ESD-generator model with 2  $\Omega$  load and 1 kV charging voltage

Figure 25: First peak current of NoiseKen ESD-generator model with 2  $\Omega$  load and 1 kV charging voltage

#### 2.1.4 TLP model

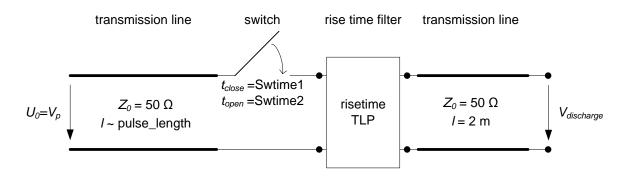

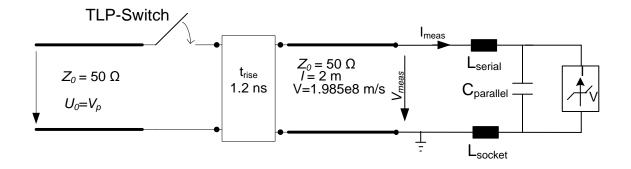

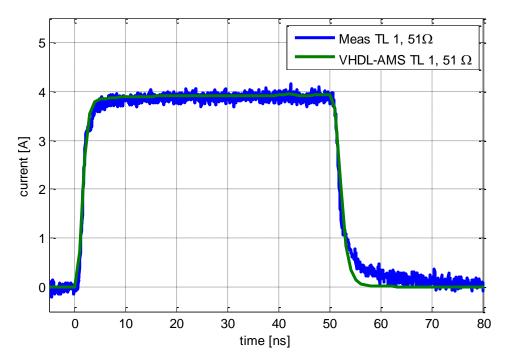

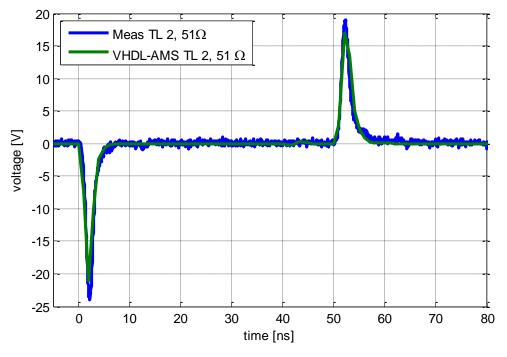

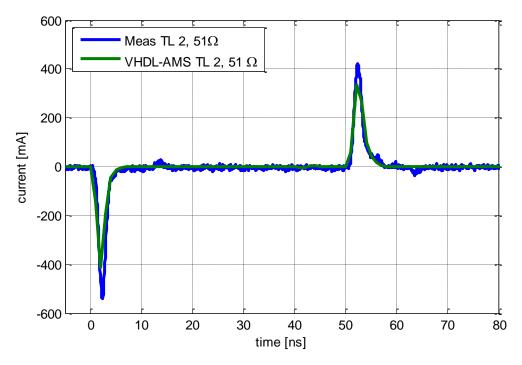

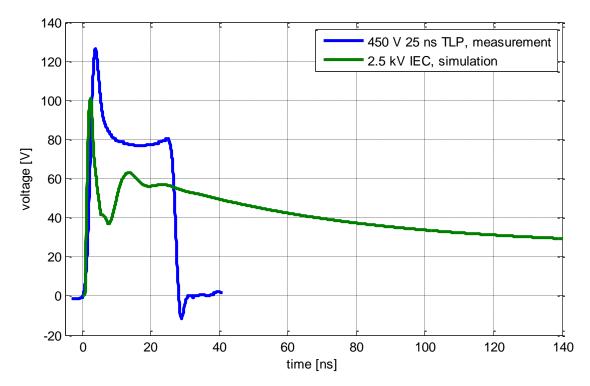

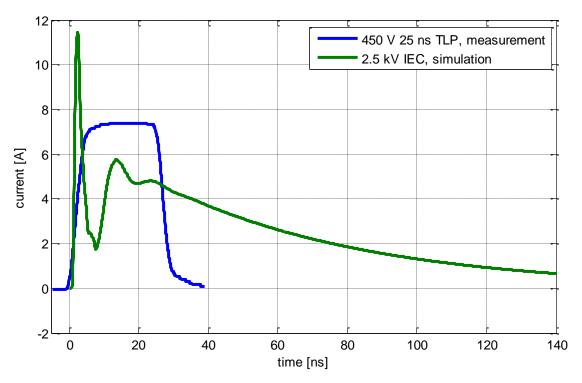

A transmission line pulser (TLP) can be used for high power characterization of ICs. In some approaches the TLP can also be applied as testing device for ESD robustness. To achieve reliable simulation results an exact modeling of the TLP is required. In comparison to the modeling of ESD-generators, some components of the used TLP [7] can be directly mapped to model components. A part of the equivalent circuit is shown in Figure 26. The model has been verified by measurement on different low and high-ohmic loads. More information can be found in [8].

Figure 26: Diagram of TLP model

The pulse amplitude and the pulse length are mainly affected by the first transmission line. For simulation a lossless VHDL-AMS transmission line model is used, where the line charge  $V_p$  can be set as an initial condition. The pulse length is adjusted defining the length of the charged line according to the following equation:

$$length = \frac{pulse\_length}{10 \text{ ns}}$$

The wave impedance  $Z_0$  is set to 50  $\Omega$ . The propagation velocity of the line is set to  $v_0 \approx 2.0 \cdot 10^8$  m/s.

The line is discharged via a relay which is considered to be an ideal switch. The rising and falling edges can be controlled by the connected rise time filter. A detailed description can be found in [9]. Three different rise times (1,2 ns, 2,0 ns or 5,0 ns) are implemented.

Finally the pulse propagates through a second 50  $\Omega$  transmission line to the DUT. In this case a VHDL-AMS model including losses is used to improve the accuracy of the simulated pulse shapes.

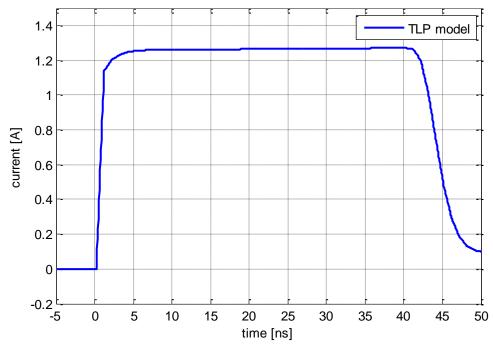

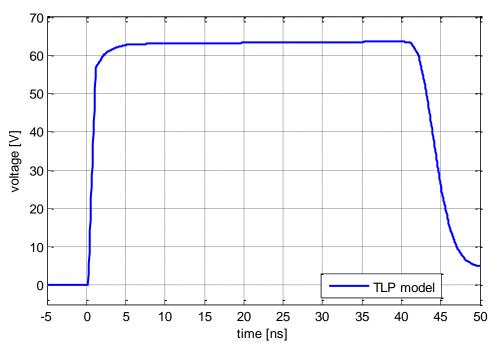

The model impedance mainly is determined by the rise time filter and the wave impedance of the transmission lines. Simulated current and voltage shapes are shown in Figure 27 and Figure 28 for a charging voltage of 1000 V and a 1,2 ns rise time filter.

Figure 27: Simulated current of discharge of the TLP model into 50  $\Omega$  with 40 ns pulse width, 1,2 ns rise time and 1 kV charging voltage

Figure 28: Simulated voltage of discharge of the TLP model into 50  $\Omega$  with 40 ns pulse width, 1,2 ns rise time and 1 kV charging voltage

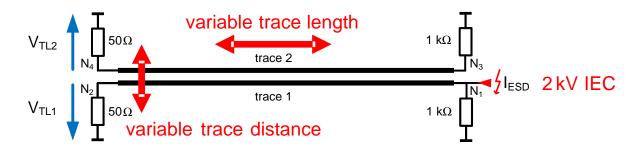

# 2.2 PCB trace model (multi conductor transmission line model)

The transmission line models used for simulation of PCB structures are described in this section.

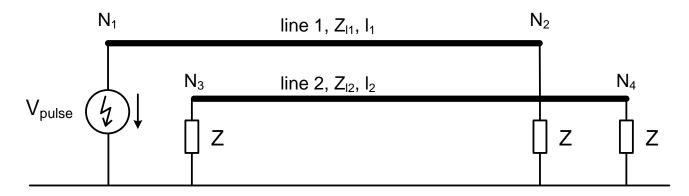

Multi conductor transmission line models can be applied for cross-talk simulation on PCBs. Detailed information on used models can be found in [10]. The simulation of

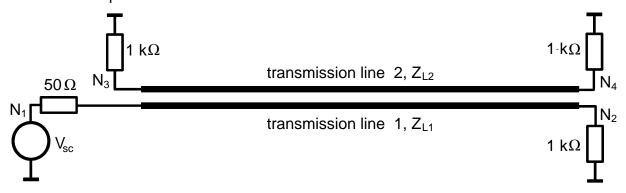

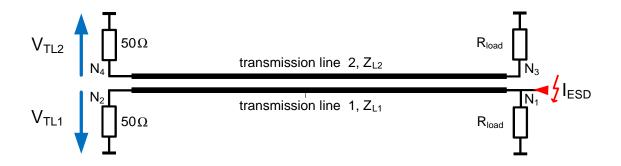

coupling effects is verified by a comparison to full wave simulation results. Figure 29 shows the equivalent circuit with two parallel conductors of equal length. A source is connected to one end of line 1. All wire endings are terminated with a 1 k $\Omega$  resistor. The source impedance is set to 50  $\Omega$ .

Figure 29: Setup for verification of transmission line models

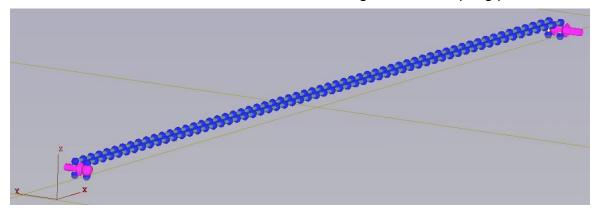

In Figure 30 the 3D full-wave model is shown. Probes were set at nodes  $N_1$ ,  $N_2$ ,  $N_3$  and  $N_4$  as indicated in Figure 29. The distance between lines is 3 mm. The length of the conductors with radius 0,3 mm is 0,2 m and height above coupling plane is 3 mm.

Figure 30: Full wave 3D simulation of transmission lines

The common mode and differential mode impedances of the transmission line configuration are extracted from the full wave model so that a similar setup can be implemented in VHDL-AMS concerning equal conductor lengths, transfer impedances and loads. Line parameters matrices are defined by the relation of the geometric configurations between transmission line 1, transmission line 2 and ground potential. The impedances can be calculated from L and C matrices. Detailed information can be found in [11].

$$L = \begin{bmatrix} 7.423\text{e-}07 & 2.819\text{e-}07 \\ 2.819\text{e-}07 & 7.422\text{e-}07 \end{bmatrix} \text{H}$$

$$C = \begin{bmatrix} 1.751\text{e-}11 & -6.653\text{e-}12 \\ -6.653\text{e-}12 & 1.752\text{e-}11 \end{bmatrix} F$$

The matrices are converted to modal parameters using transformation matrix T.

$$T = \frac{1}{\sqrt{2}} \cdot \begin{bmatrix} 1 & 1 \\ 1 & -1 \end{bmatrix}$$

$$L_{modal} = T^{-1} \times L \times T$$

$$C_{modal} = T^{-1} \times C \times T$$

The modal values are used to calculate the modal impedance matrix Z<sub>modal</sub>.

$$Z_{modal} = \sqrt{\frac{L_{modal}}{C_{modal}}}$$

The first element on the main diagonal of  $Z_{modal}$  represents  $Z_{even}$  and the second element  $Z_{odd}$ . Common mode and differential mode impedances are calculated using the following relations.

$$\mathbf{Z}_{\text{com}} = \frac{1}{2} \cdot \mathbf{Z}_{\text{even}}$$

$$Z_{\text{diff}} = 2 \cdot Z_{\text{odd}}$$

The values for  $Z_{com}$  and  $Z_{diff}$  for the given configuration were found and can be used as parameters in the VHDL-AMS model.

$$Z_{com} = 153,5 \Omega$$

$$Z_{diff} = 276,0 \Omega$$

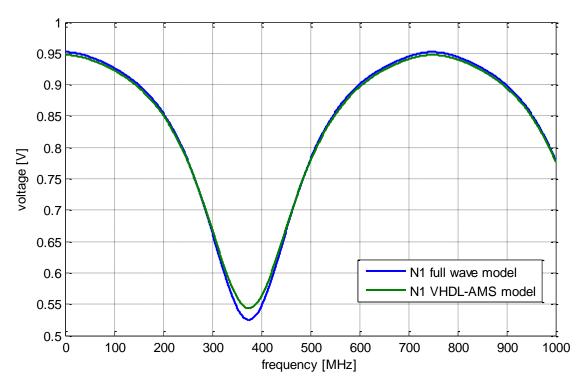

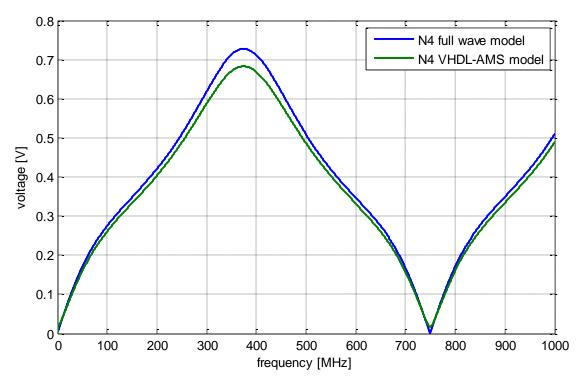

The results of both simulations are compared in Figure 31 and Figure 32 in frequency domain. Very small deviations of around 1 % between the curves of full-wave and VHDL-AMS simulation results can be seen only at resonance frequencies.

Figure 31: Comparison of VHDL-AMS and full wave simulation in frequency domain at node 1

Figure 32: Comparison of VHDL-AMS and full wave simulation in frequency domain at node 4

In Figure 33 simulated waveforms are compared for a rectangular pulse with amplitude of  $1000\,\mathrm{V}$  in time domain. Shown deviations are mainly caused by numerical problems of IFFT-algorithm of full wave solver.

Figure 33: Comparison of full wave and VHDL-AMS model in time domain at node 2

Figure 34: Comparison of full wave and VHDL-AMS model in time domain at node 3

# 2.3 Modeling of IC structures

A technique for ESD-failure modeling of IC structures is described in this section. More information can be found in [12]. In section 2.3.1 a general approach for

modeling the static and dynamic electrical behavior of unpowered ICs-pins is explained. The general technique is limited to the electrical domain. A second approach focuses on the modeling of the thermal ESD robustness of ICs is described in section 2.3.2.

The modeling approach is based on a pragmatic behavioral modeling technique without any information about IC parameters such as geometry of package, die structure, and so on.

#### 2.3.1 General modeling approach for electrical domain

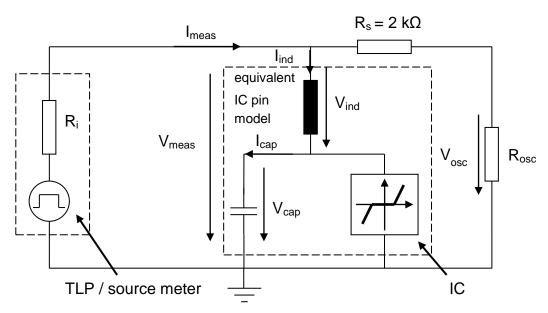

For modeling characterization data have to be measured. The IV-characteristic of a device is measured for low currents with an IV-source meter [13] and for high currents up to 60 A with a TLP [7]. In Figure 35 an equivalent circuit of the measurement setup is shown. Attenuation factors for voltage and current can be calibrated using the HPPI software. The TLP current and voltage waveforms are measured with an oscilloscope. A Tektronix CT1 current sensor is connected to measure  $I_{\rm meas}$ . An additional resistor  $R_s$  is soldered in the branch to the oscilloscope for attenuation. The voltage  $V_{\rm meas}$  can be calculated with knowledge of all attenuation factors from  $V_{\rm osc}$ .

Figure 35: Measurement setup for characterization of ICs and behavioral model for an IC pin

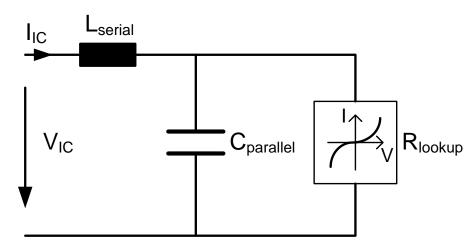

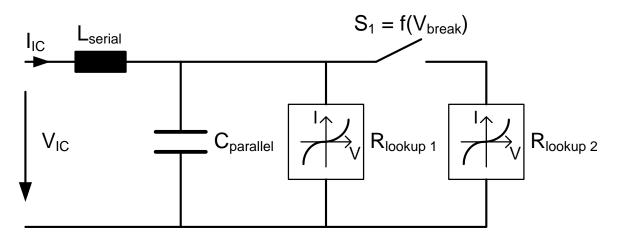

The equivalent circuit of each IC pin is composed of elements which describe the static behavior and of those which describe the dynamic behavior.

The general equivalent circuit describing the electrical domain of the IC is shown in Figure 36. The frequency dependent parameters are measured with a network analyzer to define the size of the capacitance  $C_{\text{parallel}}$  and inductance  $L_{\text{serial}}$  of an IC pin. The characteristic IV curve is composed from the source meter and TLP measurement data. The IV behavior is implemented in the model using a look-up

table function. To generate reliable measurement data minimum two equal ICs have to be tested until destruction. Deviations between the failure levels must be low. Good results were obtained with a pulse width of 100 ns. The measurement data can be extrapolated if higher amplitudes should be simulated. Due to missing verification of this model region a warning will be returned by the model.

Figure 36: IC pin model für ESD failure analysis

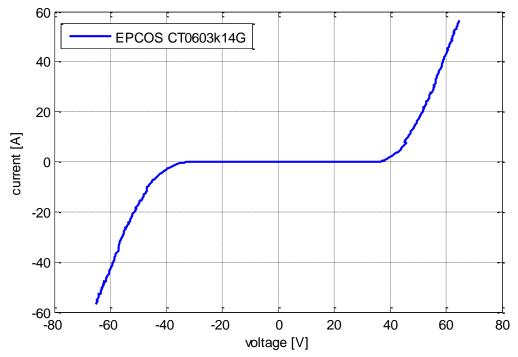

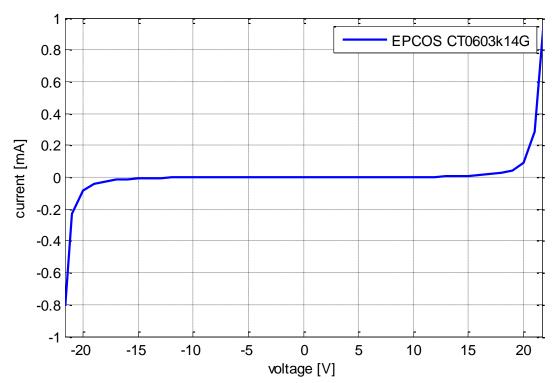

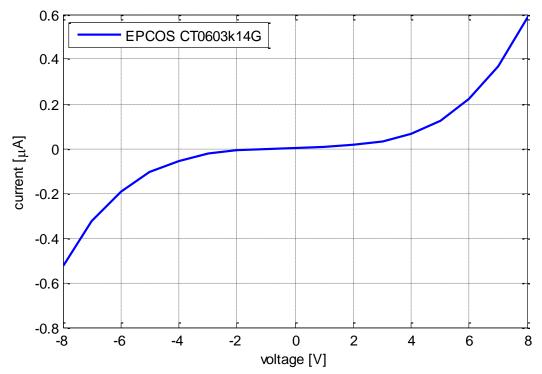

The IC pin model can also be used for modeling of ESD-protection devices. Figure 37, Figure 38 and Figure 39 show an example of a composed IV-dataset of a varistor. Data in a dynamic range from nA up to 50 A are obtained by measurement.

Figure 37: Composed varistor IV-curve

Figure 38: Composed varistor IV-curve in detail

Figure 39: Exact modeling of varistor for low voltage behavior

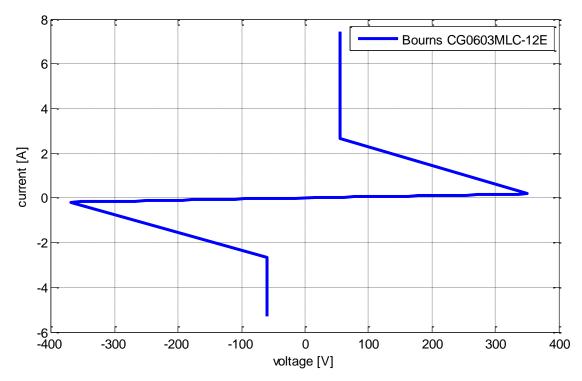

Some protection circuits show a snap-back effect. ICs can be protected using snap-back of the IV curve. If a voltage level is exceeded a breakdown of the voltage occurs. Current amplitudes are rising. The IV curve in Figure 40 shows a snap-back around 250 V for positive and negative amplitudes.

Figure 40: Measured IV characteristic of a polymer protection device

Snap-back effects cannot be implemented with a single lookup-table because of continuity problems. For modeling a second dataset has to be composed containing measurement data after the breakdown. In Figure 41 the switch S<sub>1</sub> is closed if the defined value of breakdown voltage is exceeded. A more complex implementation is possible if hysteresis functions are considered.

Figure 41: ESD protection element model with snap-back

#### 2.3.2 Thermal failure model

IC failure can often be referred either to a critical voltage or a critical temperature. In case of critical voltage a dielectric breakdown due to high local field strength inside the semiconductor occur. Here failure voltage is the critical parameter and should be

constant. Thermal failures are energy dependent. In the adiabatic region failure energy should be constant.

ESD currents flowing through the semiconductor have to be considered. The absolute active surface affected by ESD pulses usually is unknown and can only be estimated if it is assumed that total current passes through local hot spots in the semiconductor leading to destruction of the IC. Different approaches were developed to describe a power or energy dependent process leading to permanent damage condition. Wunsch-Bell described the heating of a structure as a heat source inside an infinite volume [14] [15]. Furthermore the heat flow process is assumed to be one dimensional. For rectangular pulses with duration times around 100 ns up to microseconds heat transfer from the current constriction site in the IC is assumed to be minimal.

Wunsch-Bell is based on a 2-dimensional thermal model based on power area. If all material constants are temperature-independent the specific power  $P_f$  is calculated from the following equation to reach a critical temperature  $T_c$ .

$$P_f = \sqrt{\pi \kappa \rho c_p} (T_c - T_0) \cdot t_p^{-\frac{1}{2}}$$

$\kappa$  Thermal conductivity: 30,6 W/mK (for Si)

$c_p$  Specific heat capacitance: 756,6 J/kgK (for Si)

$\rho$  Specific density: 2330 kg/m<sup>3</sup> (for Si)

$T_0$  Environment temperature: 293 K

$T_c$  Critical temperature: 1685 K

$t_p$  Pulse width: from 100 ns up to 20  $\mu$ s

Under these conditions the failure power per area decreases with increasing pulse width  $t_{\text{p}}$ . Often the critical temperature is estimated. For the investigations the melting temperature of silicon was chosen.

#### 2.3.2.1 Adiabatic RC model

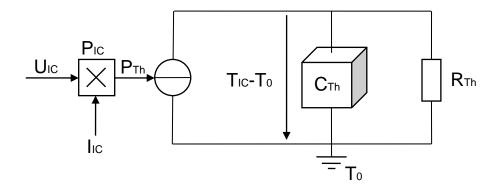

IC failure models are implemented in VHDL-AMS in thermal domain. The power at the IC pin is transformed into a heat source in thermal domain. In Figure 42 the source indicated with  $P_{th}$  is connected to a thermal capacitor  $C_{th}$  and resistor  $R_{th}$ .

Figure 42: Thermal domain of IC model

The simulated temperature rise  $T_{\Delta} = T_{IC} - T_0$  is obtained as a function of all thermal components in the circuit and from the environment temperature  $T_{0.}$

$$P_{Th} = C_{Th} \cdot \frac{dT_{\Delta}(t)}{dt} + \frac{T_{\Delta}(t)}{R_{Th}}$$

A defined critical temperature  $T_c$  is reached for a certain failure power  $P_{TLP}$  obtained from TLP measurement with the pulse width  $t_{TLP}$ . All models are based on TLP data with a selected pulse width of 100 ns because measured critical energies will change with variable pulses width. The thermal capacitance is calculated using the following equation.

$$C_{Th} = -\frac{t_{TLP}}{R_{Th} \cdot ln \left(1 - \frac{T_C - T_0}{P_{TLP} \cdot R_{Th}}\right)}$$

Dissipation is controlled by the thermal resistance  $R_{th}$  which is difficult to estimate because failed chips could not be analyzed and the active area after Wunsch-Bell may change due to local hot spots inside the semiconductor. The active area may decrease to 1/10. This means that the thermal resistance also is affected. For modeling  $R_{th}$  should be chosen in accordance with the type of the IC. Dimensions of silicon structures inside ICs with higher ESD robustness are supposed to be larger than inside "ESD-weak" ICs. Thermal resistance  $R_{th}$  therefore should be lower for extended structures and higher for smaller active areas.

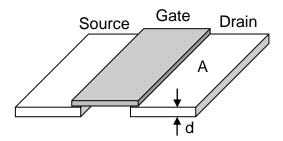

For simplification the structures in semiconductors are supposed to be in general very simple and identical like shown in Figure 43.

Figure 43: Planar structures in semiconductors

The thermal capacitance C<sub>th</sub> and resistance R<sub>th</sub> then are both dominated by the surface A. This gives another possibility to compute the thermal capacitance from material constants:

$$C_{Th} = \rho \cdot c_P \cdot A \cdot d$$

Also the thermal resistance can be calculated:

$$R_{Th} = \frac{d}{k \cdot A}$$

κ thermal conductivity

c<sub>p</sub> specific heat capacity

ρ specific density

#### 2.3.3 Scaling of the IC ESD robustness

Once the  $\mu$ C, LIN and CAN models parameters of the test chips are known and the models are verified, the thermal behavior of the models can be modified and the failure levels can be changed in order to simulate different robustness levels.

When scaling down the current-carrying capacity of semiconductor models the thermal capacity decreases. This is equivalent to a downscaling of the dimensions of the IC's ESD protection circuit which also has impact on the thermal resistance  $R_{th}$ .

To avoid unbalanced heat dissipation of failure models with scaled thermal domain, the time constant  $\tau$  of  $R_{th}$  and  $C_{th}$  is assumed to be constant:

$$\tau = R_{th}C_{th} = const$$

This means that the scaling factors are calculated related to a certain pulse energy where the scaled model is supposed to show a given failure behavior. Scaling for a new testing device or a new failure level is performed according to the following steps:

- 1. Simulate the absorbed energy at the IC pin for a new testing device or charging voltage level

- 2. Calculate the factor between the energy obtained for the new testing level and the original IC model

- 3. Divide the original thermal capacitance and resistance by the factor from (2)

### 3 Characterization of selected devices

The characterization results of selected devices for the investigations are presented in this section. Measurement and simulation data of ESD protection elements and IC pins are compared in section 3.1 and 3.2. The calculated parameters of the models with reduced ESD robustness are presented in section 3.3.

## 3.1 Selected ESD protection devices

ESD-protection devices can be soldered in parallel to the IC pins to increase the ESD robustness of a circuit. A general technique and the modeling of ESD-protection elements is described in [14].

For investigations described here 10 models (capacitor, varistors, TVS diodes) of ESD protection elements were developed. Important characteristic data of all devices is listed in Table 4.

| Туре      | Identifier                     | V <sub>clamp</sub><br>(600 V TLP) | C <sub>parallel</sub> | L <sub>serial</sub> |

|-----------|--------------------------------|-----------------------------------|-----------------------|---------------------|

| Capacitor | EPCOS 10 nF 0805 X7R           | -                                 | 10 nF                 | 1 nH                |

|           | Vishay MLV0603E30403T          | 32 V                              | 700 pF                | 3,2 nH              |

|           | TDK AVR-M1608C180M             | 33 V                              | 480 pF                | 2,7 nH              |

| Varistor  | EPCOS CT0603K14G               | 50 V                              | 120 pF                | 7,5 nH              |

|           | AVX VC060318A400               | 61 V                              | 120 pF                | 8,1 nH              |

|           | EPCOS CT0603S14AHSG            | 81 V                              | 20 pF                 | 6,7 nH              |

|           | Protek TVS GBLCS05C-LF         | 16 V                              | 3 pF                  | 5,4 nH              |

| Diode     | NEC NNCD12D-A                  | 17 V                              | 35 pF                 | 2,6 nH              |

| Diode     | Taiwan Semiconductor TSZU52C18 | 25 V                              | 20 pF                 | 2,3 nH              |

|           | Bourns CD0603-T12C             | 35 V                              | 9 pF                  | 3,4 nH              |

**Table 4: External ESD protection elements**

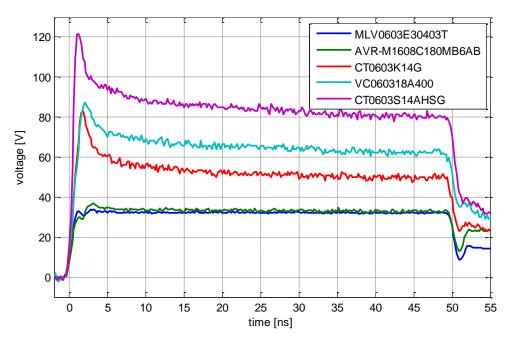

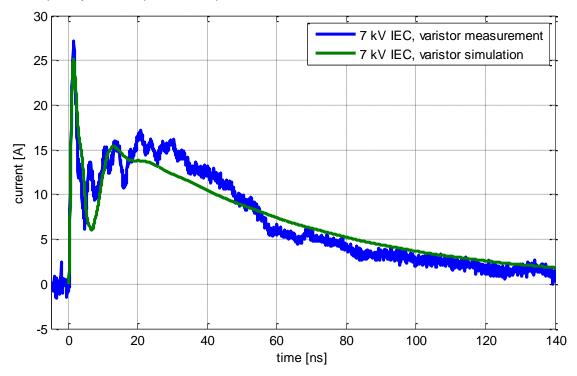

#### 3.1.1.1 Varistors

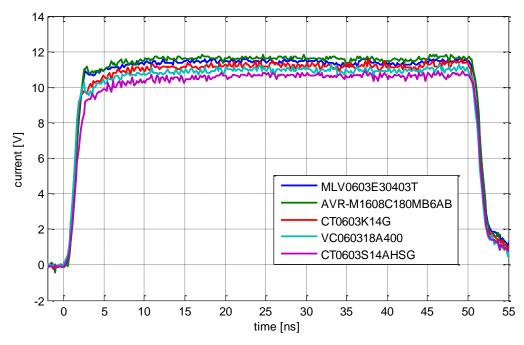

The measured voltage and current waveforms of the selected varistors are shown in Figure 44 and Figure 45. Differences in the clamping and peak voltage of more than 100 % between the curves are obtained. Deviations between current amplitudes are less than 10 %.

Figure 44: Comparison of measured voltage waveforms of different varistors for 600 V TLP charging voltage

Figure 45: Comparison of measured current waveforms of different varistors for 600 V TLP charging voltage

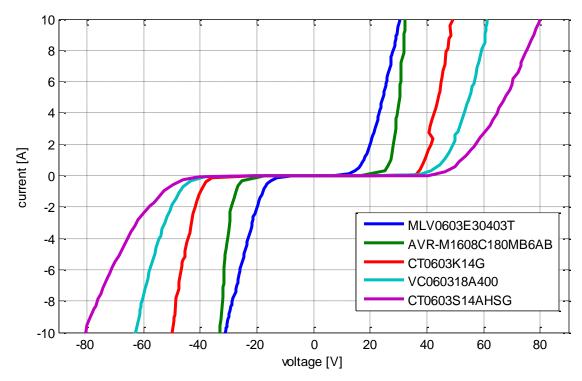

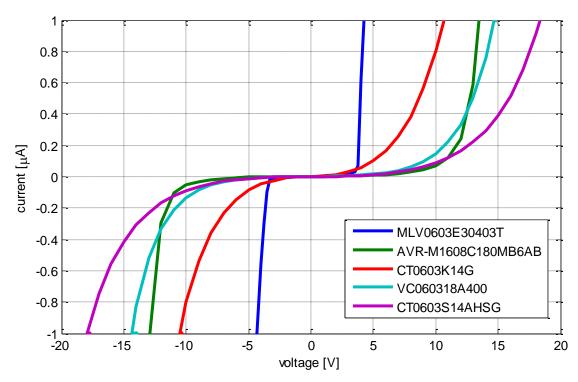

The breakdown voltages of the devices can be extracted from the IV-curves in Figure 46 and Figure 47. Although the clamping voltages of some devices are similar the breakdown voltages can be different.

Figure 46: Comparison of IV-curves of varistors measured with TLP

Figure 47: Comparison of IV-curves of varistors measured with TLP (low voltage region in detail)

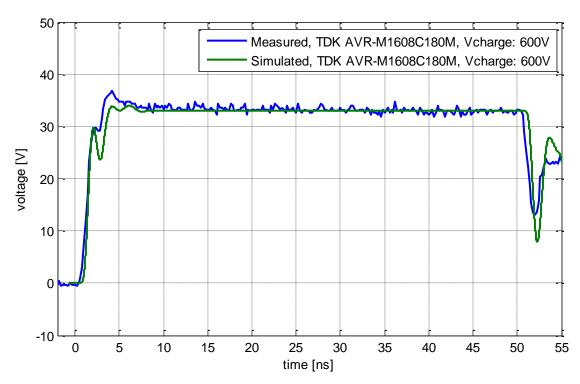

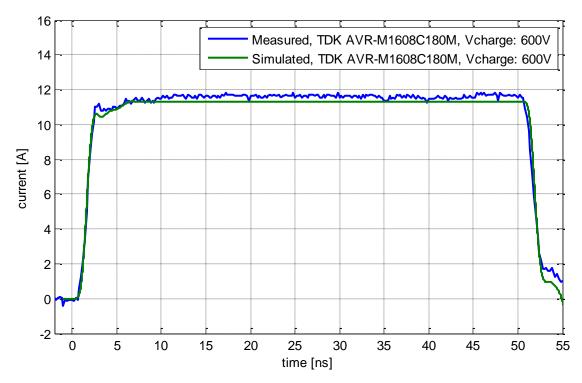

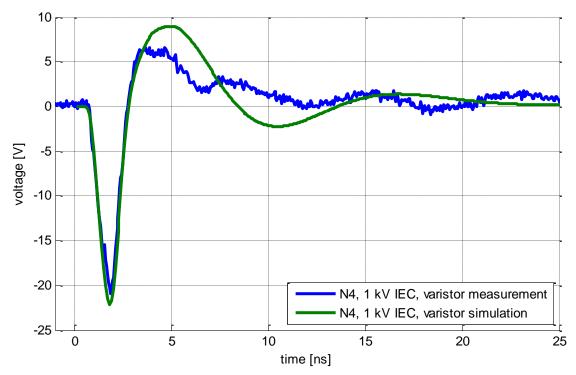

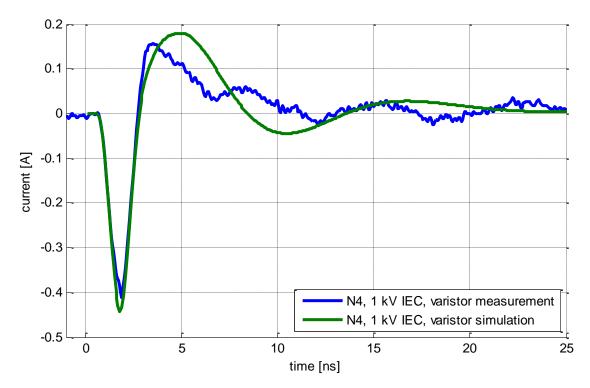

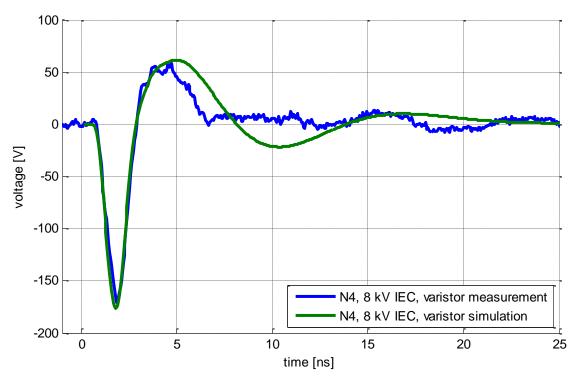

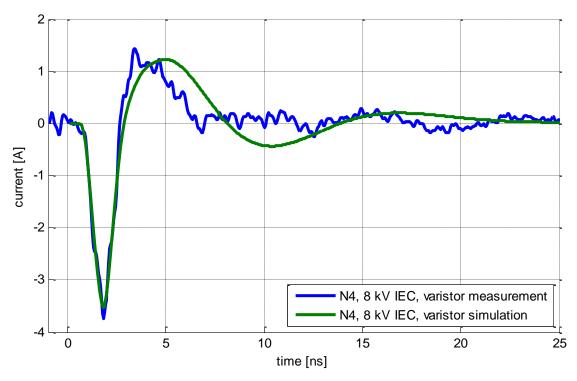

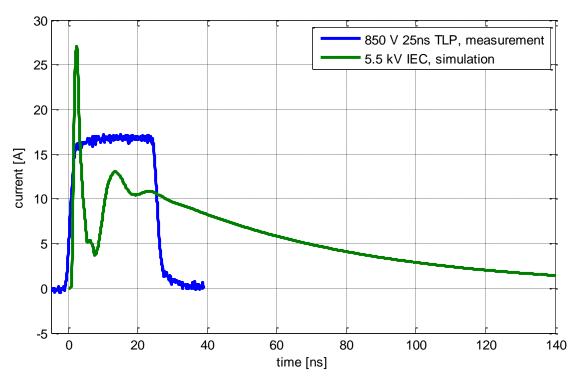

The quality of a model can be verified by simulating the TLP measurement setup. Figure 48 and Figure 49 show the voltage and current waveforms for a 600 V TLP discharge and a TDK varistor exemplarily. All rise times, fall times, and clamping behavior are modeled with less than 5 % deviation.

Figure 48: Comparison of measured and simulated TLP voltage with TDK varistor

Figure 49: Comparison of measured and simulated TLP current with TDK varistor

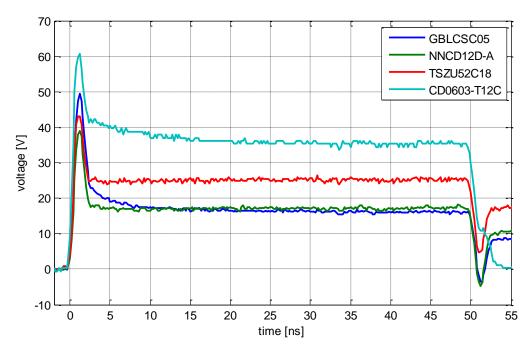

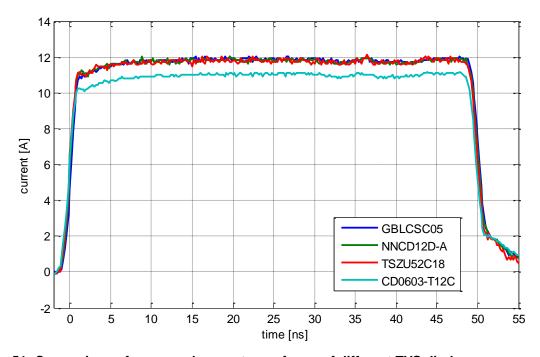

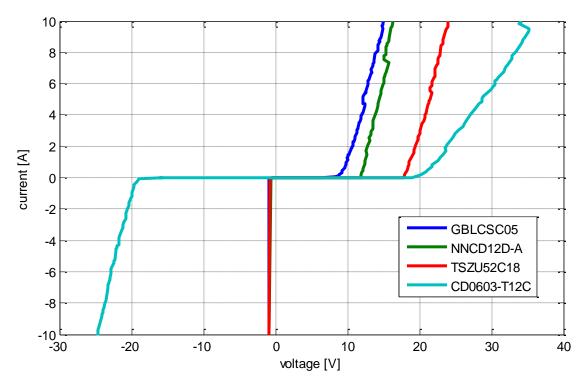

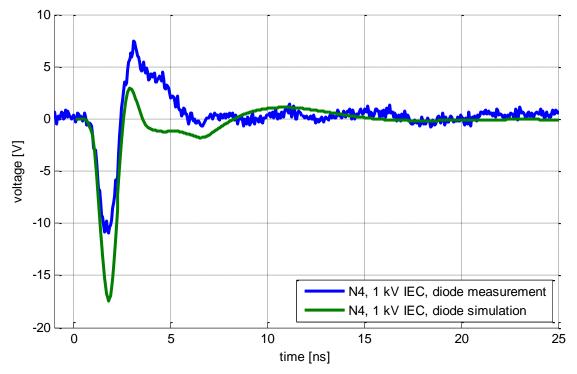

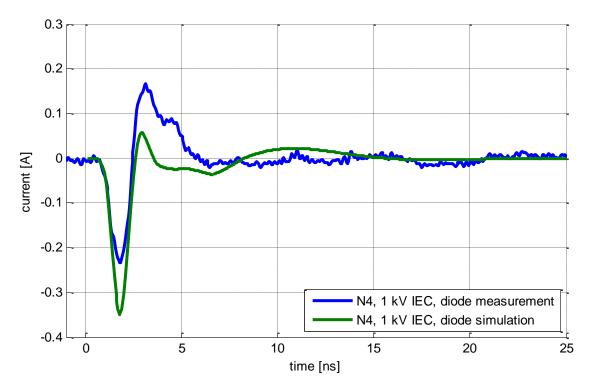

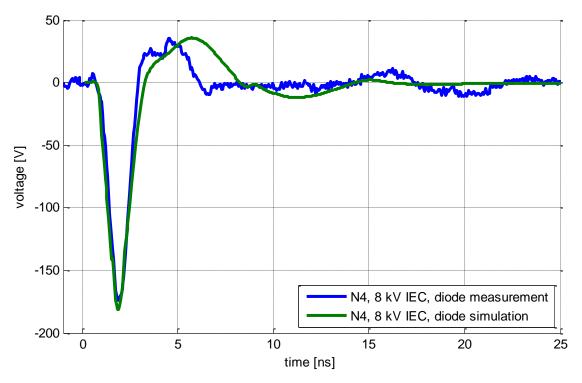

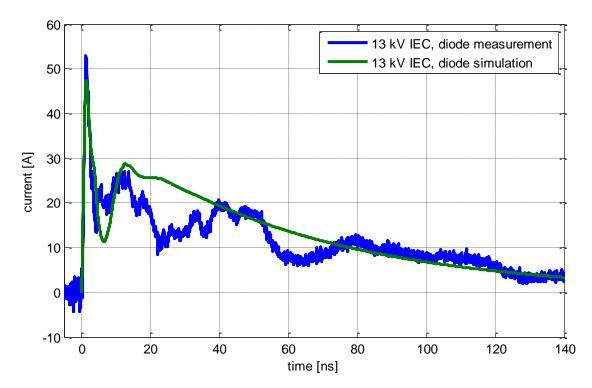

## 3.1.1.2 Diodes

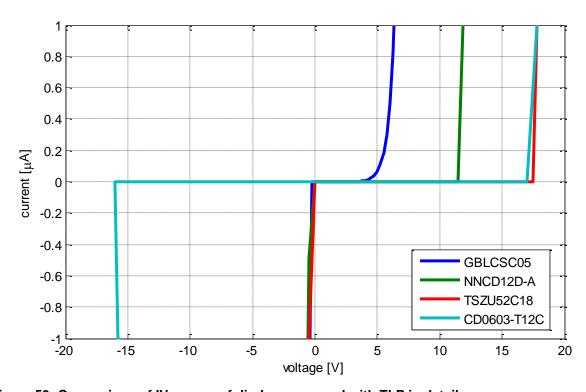

Voltage and current waveforms of the selected TVS diodes are compared in Figure 50 and Figure 51. In comparison to varistors the clamping voltage is lower. Lower

capacitances than 35 pF were measured for all diodes. The measured IV-plots show that 3 of the 4 investigated diodes are non-symmetric.

Figure 50: Comparison of measured voltage waveforms of different TVS diodes

Figure 51: Comparison of measured current waveforms of different TVS diodes

Figure 52: Comparison of IV-curves of diodes measured with TLP

Figure 53: Comparison of IV-curves of diodes measured with TLP in detail

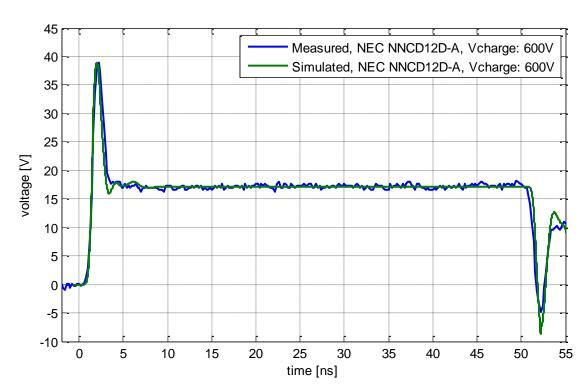

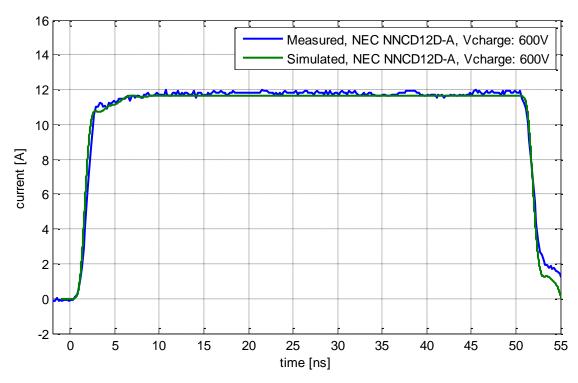

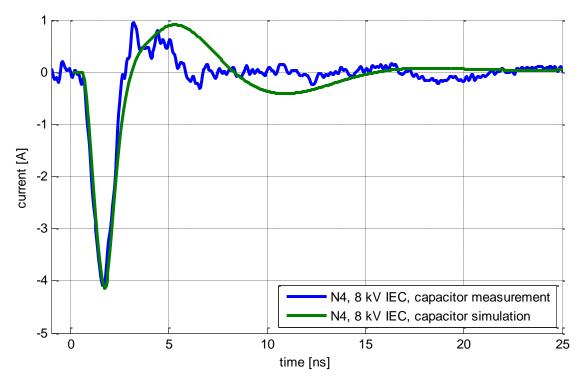

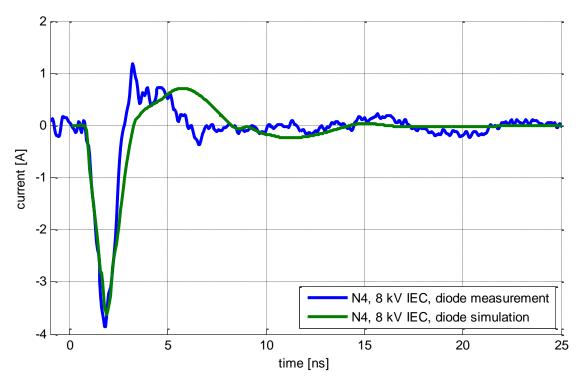

In Figure 54 and Figure 55 the measured and simulated waveforms with an NEC diode connected to the TLP setup are plotted. Good accuracy with less than 5 % deviation is obtained for TVS diode models.

Figure 54: Comparison of measured and simulated voltage at NEC TVS diode

Figure 55: Comparison of measured and simulated current at NEC TVS diode

# 3.2 Characterization of selected IC pins with TLP

The characterization data for the selected IC pins is measured with two measurement setups. The TLP measurement setup shown in section 3.2.1 was used in time domain. A frequency domain setup with a network analyzer is described in

section 3.2.2. In the following sections 3.2.3, 3.2.4 and 3.2.5 waveforms and IV curves are presented for a LIN ATA6662C transceiver, CAN TJA1041T transceiver and a XC864 microcontroller. For verification of the measurement data and the created model simulated and measured waveforms are compared.

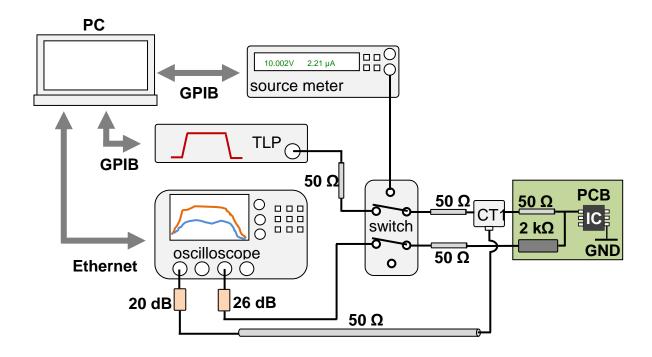

# 3.2.1 Time domain measurement setup

The time domain characterization setup shown in Figure 56 is controlled via a PC which is connected to the TLP unit, a fast 6 GHz 20 GS/s oscilloscope, and a source meter with minimal current resolution of 10 pA. All instruments are connected to the test board by a switch.

Figure 56: Measurement setup for IC characterization

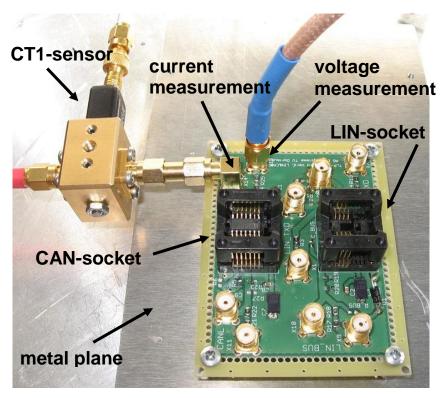

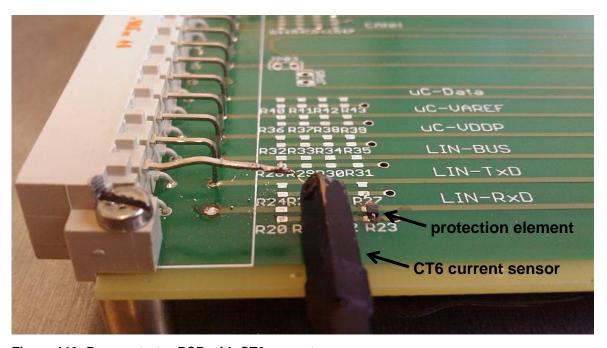

For the investigations two test boards were developed. On the board shown in Figure 57 selected socket pins for CAN and LIN transceivers are connected via short traces to SMA connectors for measurement. Each selected pin for characterization is independent so that all SMA connectors are left open on the board except two used for measurement. Current is measured with a CT1 current sensor. Voltage and current amplitudes are attenuated by minimum 20 dB in order to protect measurement devices.

Figure 58 shows the equivalent test board with a socket for the  $\mu$ C. During measurement the PCBs were screwed on a metal plane to ensure adequate grounding conditions.

Figure 57: TLP measurement setup with PCB for LIN and CAN transceivers

Figure 58: TLP board with µC socket

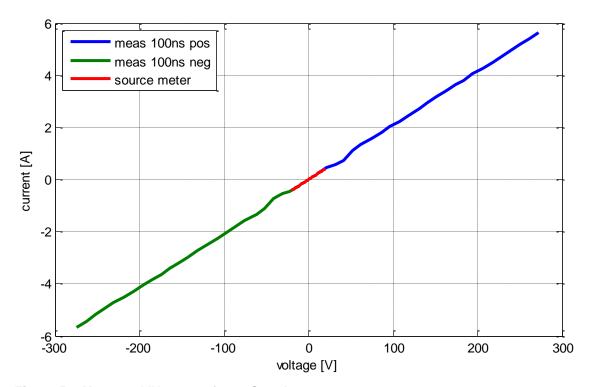

The settings of the TLP measurement setup are calibrated using a resistor. In Figure 59 the IV curves measured with TLP and source meter for a 47  $\Omega$  resistor are compared. The curve consists of 2 TLP datasets and 1 dataset from source meter. For low charging voltages of the TLP some deviations may occur because of high attenuation factors. Precise results are obtained for high charging voltages.

Figure 59: Measured IV curve of a 47  $\Omega$  resistor

As a first step for IC testing a TLP sweep with negative and positive charging voltages is done to estimate the negative and positive breakdown voltages of the ESD structures. Then the static behavior is measured with the source meter till 95 % of the estimated breakdown voltage is reached. Breakdown voltage of an IV curve is defined where the current increases more than 10 % compared to the preceding voltage step. From the measured curve a characteristic point is also selected at about 90 % of the defined breakdown voltage. This current at the characteristic point will be monitored after each TLP discharge which is major criteria for destruction of an IC. Permanent IC damage generally is assumed if a DC current measurement at a voltage level before the characteristic point exceeds the initially measured values by a factor of ten.

The failure energies are determined with changing voltage amplitude until destruction of the IC is detected with IV curve measurements. The increment of the charging voltage should be selected dynamically to minimize pre-damaging. Smaller voltage steps are applied close to the level of breakdown voltage which is an first estimation for the failure level.

### 3.2.2 Frequency domain measurement setup

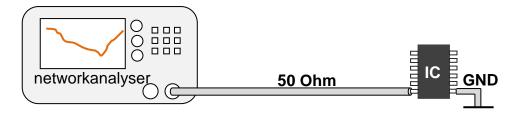

S-parameters are measured with a network analyzer (NWA) according to Figure 60. For more accuracy TLP testboards were used without sockets. The NWA was calibrated by soldering open short and load SMD devices on the PCB close to the IC soldering pads. Values for the pin capacitance C are calculated from S11 parameters at 10 MHz and for pin inductance L at about 1GHz.

Figure 60: Setup for IC characterization in frequency domain

# 3.2.3 Characterization of LIN transceiver ATA6662C TxD pin

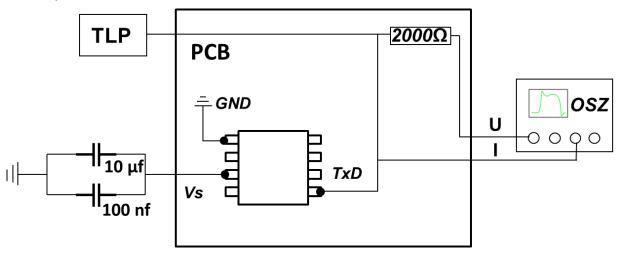

In Figure 61 the schematic of the measurement setup is shown. 10  $\mu$ F and 100 nF capacitors are connected to  $V_s$  pin in order to obtain realistic conditions for failure model parameter measurements.

Figure 61: Schematic of TLP measurement setup for LIN ATA6662C TxD pin

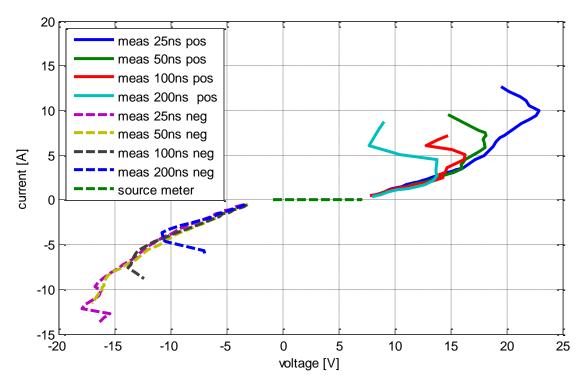

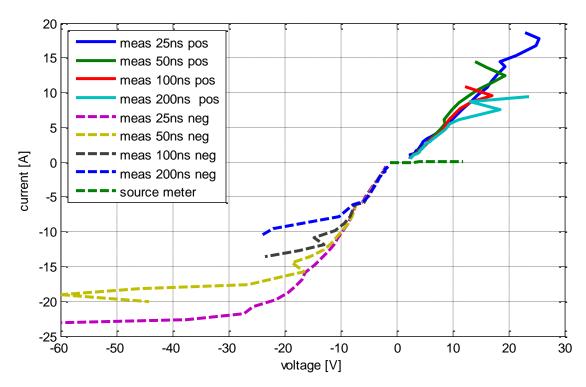

The IV curves for the LIN TxD pin are shown in Figure 62. Measurement data up to about 13 A were measured for 25 ns pulse width. Beside from the measured DC spot current yet the last points of each IV curve indicate destruction of the IC because of a significant voltage drop.

Figure 62: Comparison of measured IV characteristics for LIN TxD pin

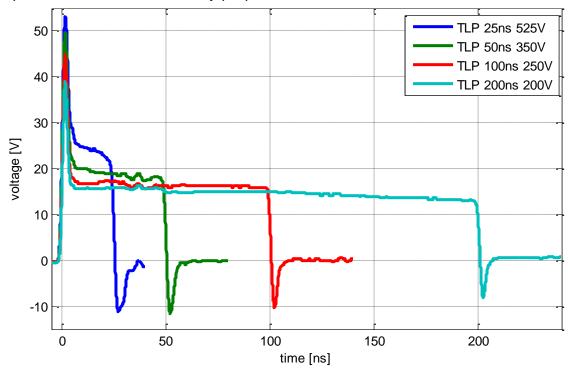

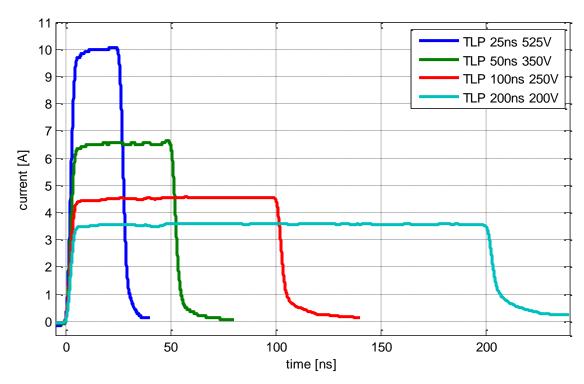

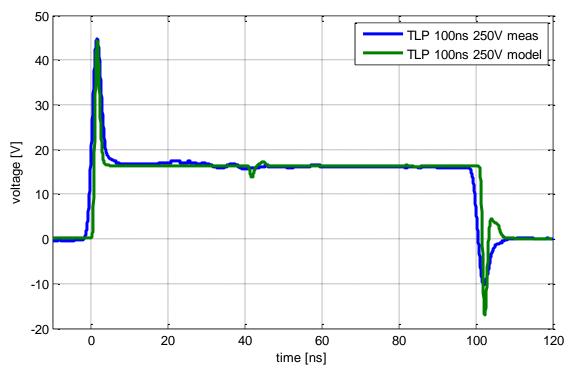

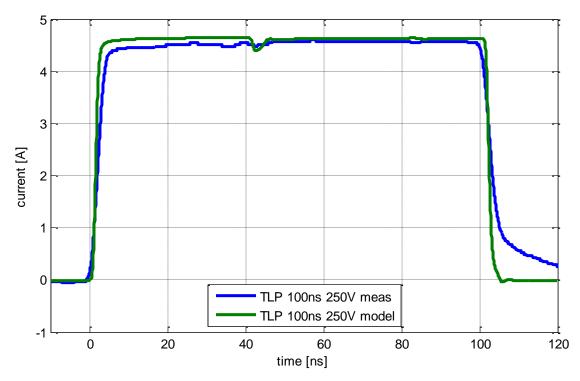

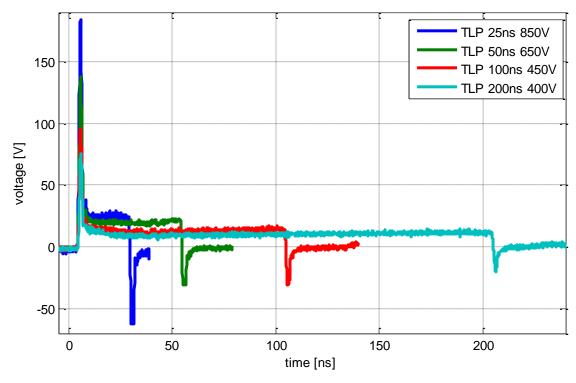

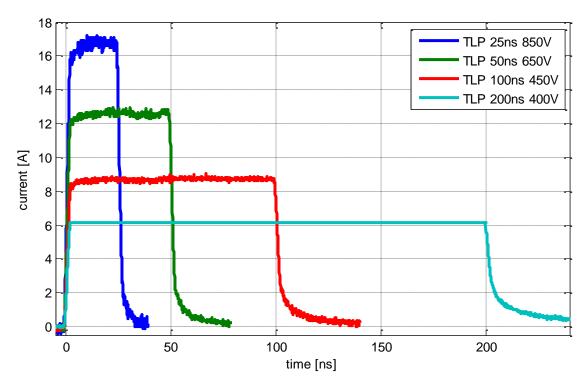

In Figure 63 and Figure 64 the critical waveforms are compared for different pulse widths for positive TLP charging voltages before destruction. TLP charging voltage and pulse width behave inversely proportional.

Figure 63: Critical positive voltage waveforms for different pulse widths at LIN TxD pin

Figure 64: Critical positive current waveforms for different pulse widths at LIN TxD pin

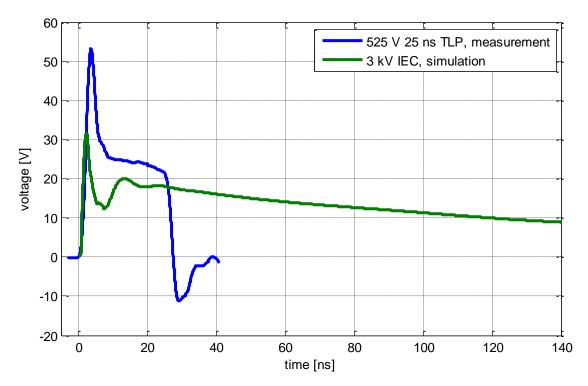

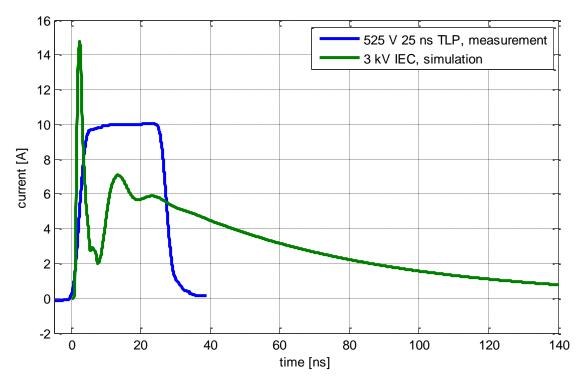

Table 5 summarizes the parameters from the curves. Maximum charging voltage was 525 V where a peak voltage of 53 V and a peak current of 10 A were measured. The energy can be calculated from current and voltage waveforms. For many IC-pins an increasing critical energy can be found with increasing pulse width. This fact can be explained by heat dissipation before the pulse has decayed which is especially true for 200 ns pulses.

| IC (PIN)          | t <sub>TLP</sub><br>[ns] | V <sub>TLP</sub><br>[V] | V <sub>max</sub><br>[V] | I <sub>max</sub><br>[A] | V <sub>mean</sub><br>[V] | I <sub>mean</sub><br>[A] | E <sub>crit</sub><br>[µJ] |

|-------------------|--------------------------|-------------------------|-------------------------|-------------------------|--------------------------|--------------------------|---------------------------|

| 1 151             | 25                       | 525                     | 53.2                    | 10.0                    | 22.9                     | 10                       | 5.8                       |

| LIN-              | 50                       | 350                     | 49.7                    | 6.6                     | 18                       | 6.5                      | 6.1                       |

| ATA6662C<br>(TXD) | 100                      | 250                     | 44.8                    | 4.6                     | 16.2                     | 4.6                      | 7.4                       |

|                   | 200                      | 200                     | 39.0                    | 3.6                     | 13.7                     | 3.6                      | 10.4                      |

Table 5: Measured parameters with variation of TLP pulse width for LIN TxD pin

All parallel IC-capacitances C and serial IC-package-inductances L for modeling were measured with a network analyzer without a bias voltage. Table 6 contains the results for LIN TxD pin. Measurement data in frequency domain was measured without additional capacitors connected to the IC pins.

| IC (PIN) | C <sub>parallel</sub> | L <sub>serial</sub> |

|----------|-----------------------|---------------------|

| TXD      | 8,5 pF @ 10 MHz       | 2,5 nH @ 1,1 GHz    |

Table 6: Measured values  $L_{serial}$  and  $C_{parallel}$  for LIN TxD pin

#### 3.2.3.1 Verification of LIN model

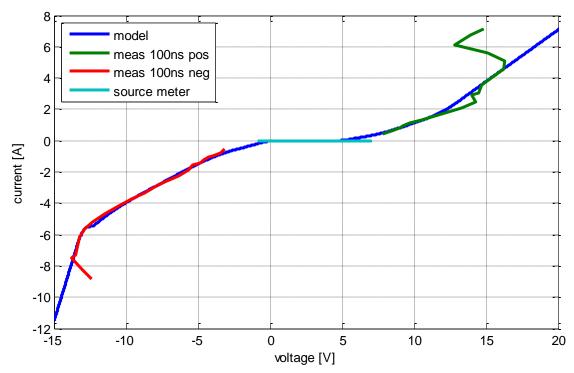

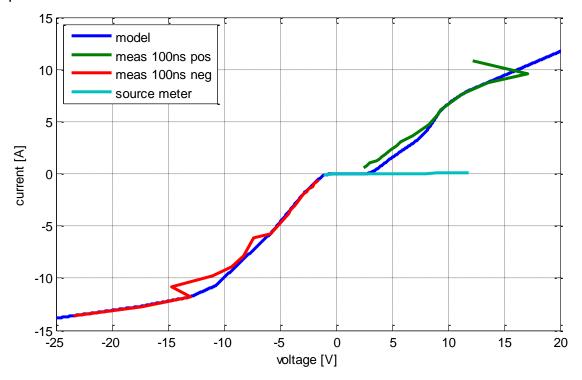

The measured and the modeled IV curves are compared in Figure 65. For the extension of the model's applicability the IV curve was extrapolated.

Figure 65: Comparison of measured and simulated IV curves of LIN TxD pin

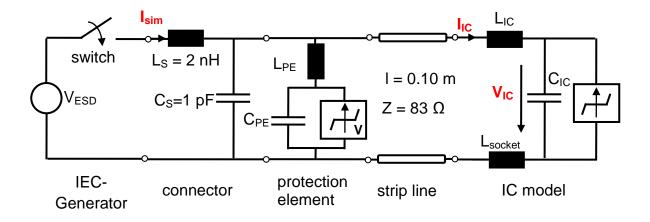

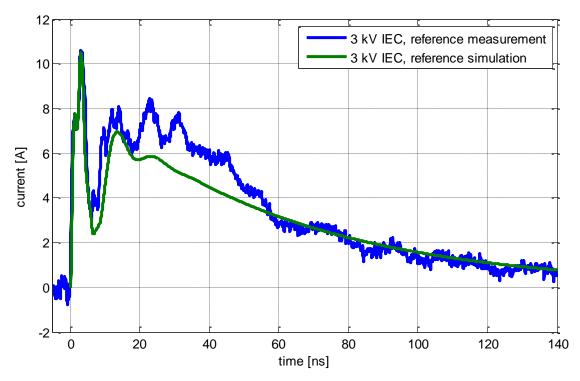

The model is verified by a comparison of TLP measurement data and simulation of the TLP measurement setup including the IC model. A schematic of the setup is given in Figure 66 for the LIN TxD pin. Beside the TLP model described in section 2.1.4 a 10 nH inductor was added representing the inductance of the socket connected with the TLP testing board in the current return path of the IC.

Figure 66: Setup for verification of measured data by simulation

The curves presented in Figure 67 and Figure 68 for 100 ns pulse width show a good matching. The voltage peak is simulated well. For a more accurate modeling of the setup additional parasitic elements should be considered.

Figure 67: Comparison of measured and simulated voltage at LIN TxD pin

Figure 68: Comparison of measured and simulated current at LIN TxD pin

# 3.2.4 Characterization of CAN transceiver TJA1041T CANH pin

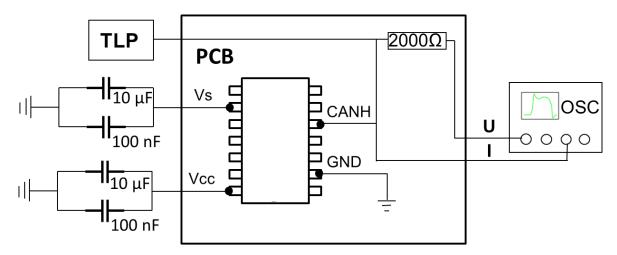

Similar to the LIN transceiver 10  $\mu$ F and 100 nF capacitors were connected to the Vs and Vcc pin during TLP measurement. A circuit diagram is given in Figure 69.

Figure 69: Circuit diagram of TLP measurement setup for CAN TJA1041T CANH pin

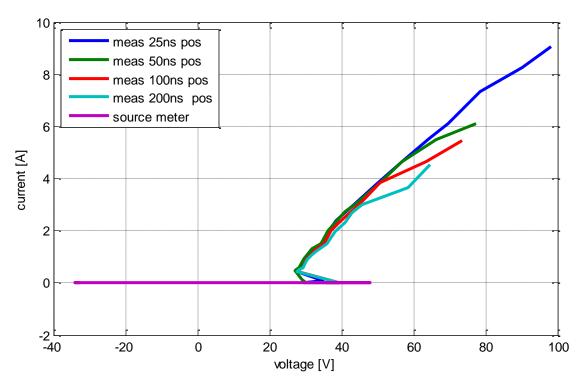

The overlaying IV curves of the selected CANH pin are shown in Figure 70 for positive charging voltages. Destruction was detected for all pulse widths.

Figure 70: Comparison of measured IV-characteristics for CANH pin

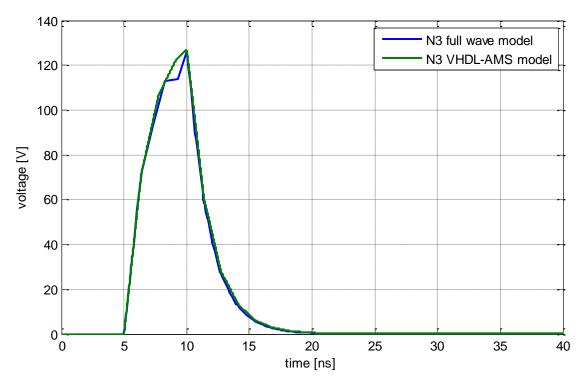

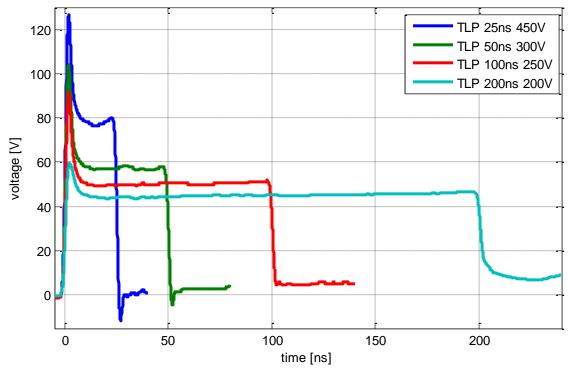

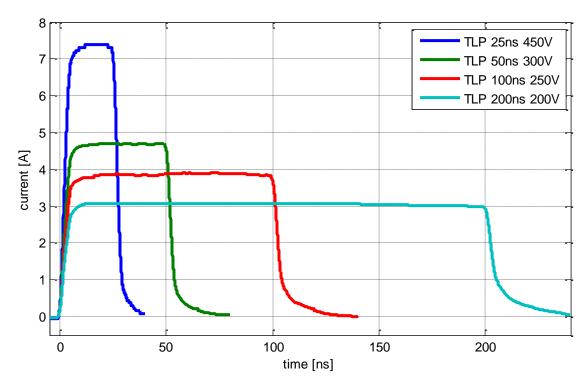

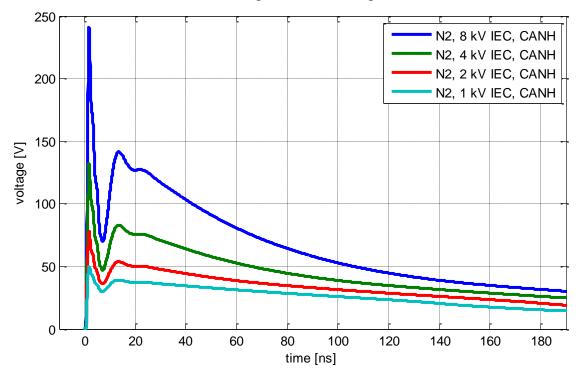

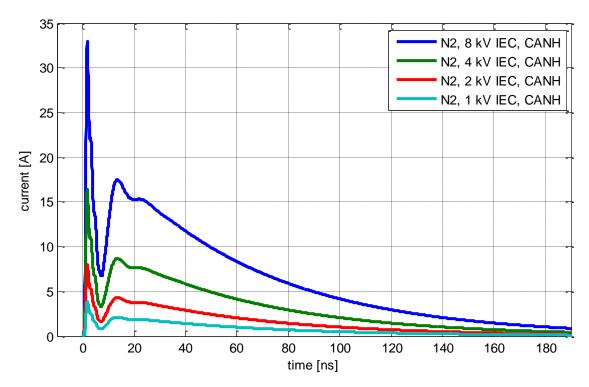

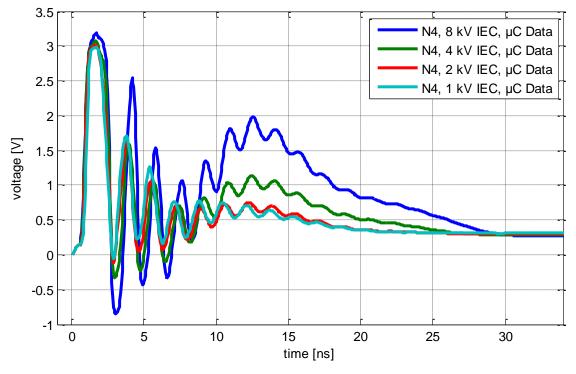

The positive critical curve shapes of TLP pulses for the CANH pin are shown in Figure 71 and in Figure 72. Table 7 includes all measured amplitudes and energies for the selected pulse widths. The highest amplitudes before destruction is detected is about 126 V and 7,3 A. Similar to LIN TxD the calculated energies differ by a factor of 2 for 25 ns and 200 ns pulses.

Figure 71: Critical positive voltage waveforms for different pulse widths at CANH pin

Figure 72: Critical positive current waveforms for different pulse widths at CANH pin

| IC (PIN)                   | t <sub>TLP</sub><br>[ns] | V <sub>TLP</sub><br>[V] | V <sub>max</sub><br>[V] | I <sub>max</sub><br>[A] | V <sub>mean</sub><br>[V] | I <sub>mean</sub><br>[A] | E <sub>crit</sub><br>[µJ] |

|----------------------------|--------------------------|-------------------------|-------------------------|-------------------------|--------------------------|--------------------------|---------------------------|

| CAN-<br>TJA1041T<br>(CANH) | 25                       | 450                     | 126.5                   | 7.3                     | 78.5                     | 7.3                      | 13.6                      |

|                            | 50                       | 300                     | 104.1                   | 4.7                     | 56.7                     | 4.6                      | 13.1                      |

|                            | 100                      | 250                     | 91.8                    | 3.9                     | 50.6                     | 3.9                      | 19.2                      |

| , ,                        | 200                      | 200                     | 59.5                    | 3.0                     | 45.7                     | 3                        | 27.5                      |

Table 7: Measured parameters with variation of TLP pulse width for CANH pin

In frequency domain a capacitance of 10,5 pF and inductance of 4,5 nH was measured for the CANH pin.

| IC (PIN) | C <sub>parallel</sub> | L <sub>serial</sub> |

|----------|-----------------------|---------------------|

| CANH     | 10,5 pF @ 10 MHz      | 4,5 nH @ 1 GHz      |

Table 8: Measured values for  $L_{\text{serial}}$  and  $C_{\text{parallel}}$  for CANH pin

## 3.2.4.1 Verification of CAN model

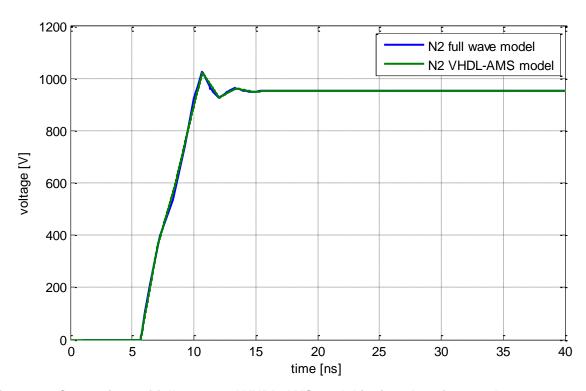

In Figure 73 measurement results and a simulated IV curve of the CANH pin are compared. Good matching can be obtained for positive and negative TLP charging voltages. The corresponding TLP simulation for 100 ns pulse width can be found in Figure 74 and Figure 75. L<sub>socket</sub> was set to 18 nH.

Figure 73: Comparison of measured and implemented IV-curves of CANH pin

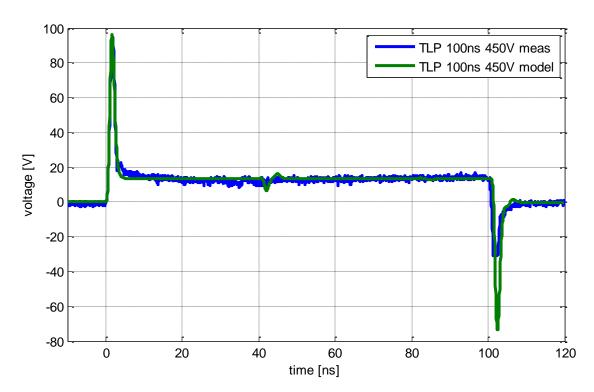

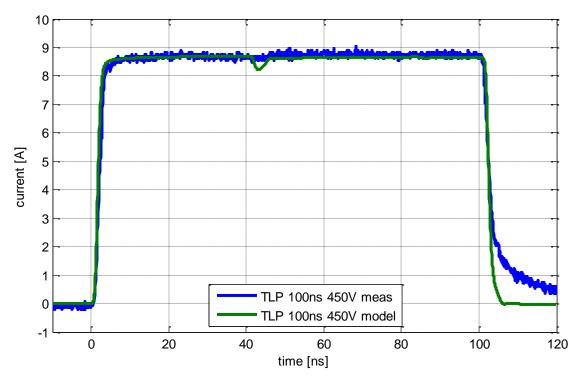

Figure 74: Comparison of simulated and measured voltage for positive TLP charging voltage at CANH pin

Figure 75: Comparison of simulated and measured current for positive TLP charging voltage at CANH pin

# 3.2.5 Characterization of µC XC864 DATA pin

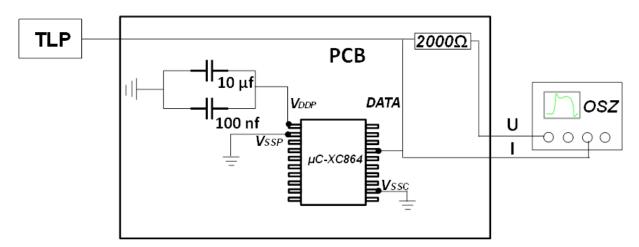

Characterization and modeling results are described for the DATA pin of the XC864 microcontroller in this section. 10  $\mu$ F and 100 nF capacitors were soldered in parallel to the VDDP pin during the TLP test as shown in Figure 76.

Figure 76: Circuit diagram of TLP measurement setup for XC864 DATA pin

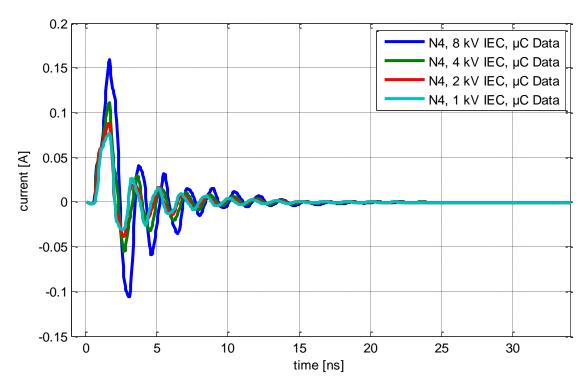

Measured IV curves of the DATA pin are compared in Figure 77. The pin turns out to be fail at current amplitudes of less than minus 20 A. In comparison to the characteristic of CAN and LIN transceiver pins the failure voltage of the DATA pin is quite low.

Figure 77: Comparison of measured IV-characteristics for DATA pin of  $\mu C$

In the plots comparing critical voltage over pulse width for positive TLP charging voltages the clamping voltage of all curves is about 20 V. In Figure 78 a slight rise of the voltage can be observed with progress of the TLP pulse. This could be caused by heating effects in the current path of the IC.

Figure 78: Critical positive voltage waveforms for different pulse widths at DATA pin of XC864

Figure 79: Critical positive current waveforms for different pulse widths at DATA pin of XC864

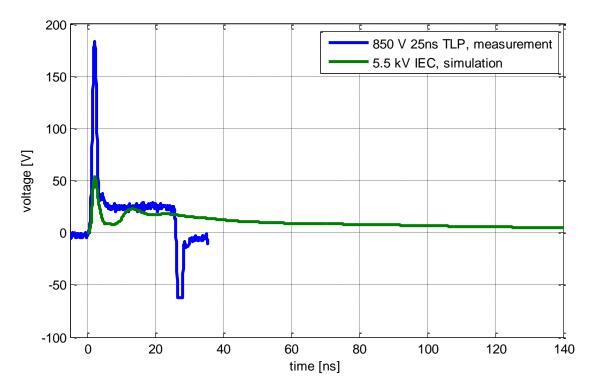

The maximum TLP charging voltage before destruction was 850 V. The highest voltage and current amplitudes of all tested ICs are reached at about 183 V and 17 A. The calculated critical energy from the pulses was found to be very stable.

| IC (PIN) | t <sub>TLP</sub><br>[ns] | V <sub>TLP</sub><br>[V] | V <sub>max</sub><br>[V] | I <sub>max</sub><br>[A] | V <sub>mean</sub><br>[V] | I <sub>mean</sub><br>[A] | E <sub>crit</sub><br>[µJ] |

|----------|--------------------------|-------------------------|-------------------------|-------------------------|--------------------------|--------------------------|---------------------------|

|          | 25                       | 850                     | 183.7                   | 17.2                    | 24.9                     | 16.7                     | 12.7                      |

| μC-XC864 | 50                       | 650                     | 138.1                   | 12.9                    | 19.3                     | 12.5                     | 13.9                      |

| (DATA)   | 100                      | 450                     | 95.4                    | 9.0                     | 13.5                     | 8.7                      | 12.3                      |

|          | 200                      | 400                     | 75.2                    | 6.1                     | 11.1                     | 6.1                      | 13.3                      |

Table 9: Measured parameters with variation of TLP pulse width for µC DATA pin

$C_{\text{parallel}}$  and  $L_{\text{parallel}}$  are set to 7,6 pF and 9,2 nH in the model.

| IC (PIN)       | C <sub>parallel</sub> | L <sub>serial</sub> |

|----------------|-----------------------|---------------------|

| μC_XC864(DATA) | 7,6 pF @ 10 MHz       | 9,2 nH @ 1,2 GHz    |

Table 10: Measured values  $L_{serial}$  and  $C_{parallel}$  for XC864  $\mu C$

# 3.2.5.1 Verification of µC model

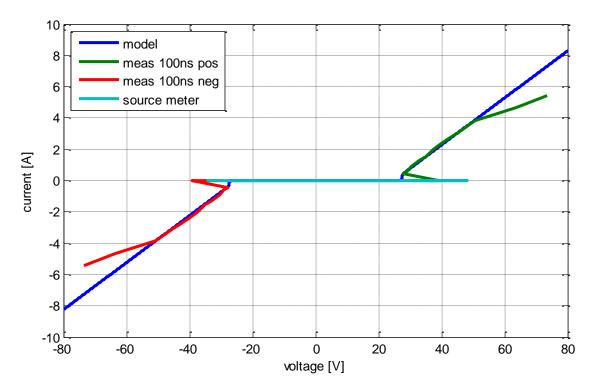

In Figure 80 the simulated and measured IV characteristics are compared for 100 ns pulse width.

Figure 80: Comparison of measured and implemented IV-curves of µC DATA pin

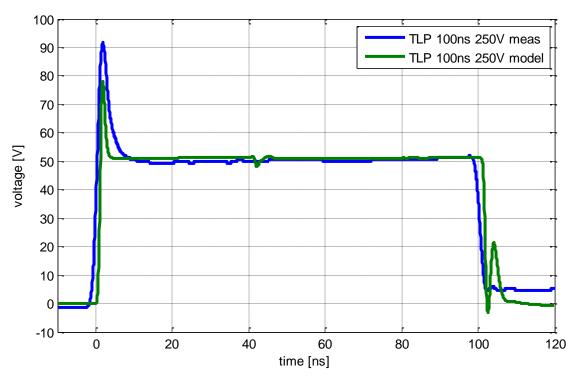

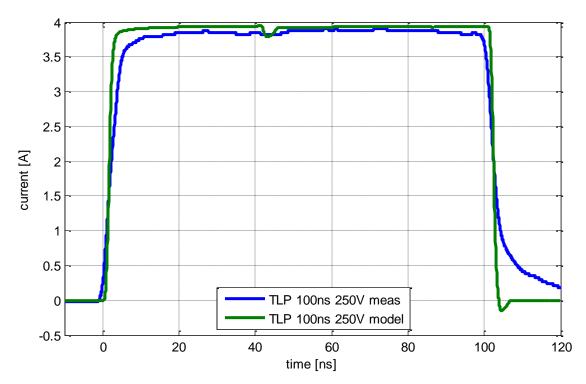

A good matching was obtained comparing simulation and measurement data in Figure 81 and Figure 82. L<sub>socket</sub> was set to 18 nH.

Figure 81: Comparison of simulated and measured voltage for positive TLP charging voltage at DATA pin of XC864  $\mu\text{C}$

Figure 82: Comparison of simulated and measured current for positive TLP charging voltage at DATA pin of XC864  $\mu\text{C}$

## 3.3 ICs with lower ESD robustness

The impact of ESD coupling on ICs with lower ESD robustness is investigated based on simulation. The ESD robustness of the models presented and verified in section 3.2 is modified according to the method described in section 2.3.3. The scaling method is based on the concept of a critical energy when IC pins might be destroyed. The calculated failure energies at the IC pin causes a temperature rise up to critical values.

#### 3.3.1 IEC robustness factor 0,5

In Table 11 the failue energies and necessary charging voltages of an IEC ESD generator are shown. The voltage for which the critical temperature can be calculated was simulated using the IC model described in section 3.2. A new critical energy was simulated by setting half of the charging voltage of the measured value. Because the temperature rise is sensitive to small changes of the values a deviation of some degrees K has to be accepted. Because of the resistive IV characteristic of the ICs the scaling factor corresponding to the failure energy usually is different from the factor used for the charging voltage.

| IC                     | IEC-failure<br>simulation [kV] |       | failure e | energy [µJ] | failure<br>temperature [K] |       |

|------------------------|--------------------------------|-------|-----------|-------------|----------------------------|-------|

|                        | reference                      | IEC/2 | reference | IEC/2       | reference                  | IEC/2 |

| μC-XC864<br>(DATA)     | 4,55                           | 2,27  | 13        | 3,8 (3,42)  | 1711                       | 1709  |

| LIN-ATA662C<br>(TXD)   | 3,0                            | 1,5   | 8,1       | 2,91 (2,78) | 1695                       | 1687  |

| CAN-TJA1041T<br>(CANH) | 2,9                            | 1,45  | 22,19     | 8,09 (2,74) | 1704                       | 1701  |

Table 11: Calculated factors for IEC/2 ESD robustness scaling

The minimal failure energy is 2,91  $\mu J$  and was calculated for the LIN transceiver. A bisection of the IEC ESD robustness voltage results in a scaling factor of about 3 for the energy. The corresponding values for the thermal capacitance  $C_{th}$  and resistance  $R_{th}$  are summarized in Table 12. Because the ESD robustness is reduced,  $C_{th}$  has to be reduced too. The active area inside the semiconductor is getting smaller which causes increasing thermal resistance because heat dissipation depends on surface effects.

| IC                     | therm. capac | itance [nJ/K] | therm. resistance [K/W] |       |  |

|------------------------|--------------|---------------|-------------------------|-------|--|

| .0                     | reference    | IEC/2         | reference               | IEC/2 |  |

| μC-XC864 (DATA)        | 8.87         | 2.59          | 730                     | 2497  |  |

| LIN-ATA662C (TXD)      | 5.37         | 1.93          | 470                     | 1308  |  |

| CAN-TJA1041T<br>(CANH) | 13.9         | 5.07          | 91                      | 249   |  |

Table 12: Thermal capacitance and resistance for IC pins with IEC/2 ESD robustness

## 3.3.2 HBM robustness factor 0,5

In Table 13 and Table 14 all parameters are given for a bisection of the HBM robustness. The reference values were simulated using the HBM model described in section 2.1.1. Similar scaling factors were calculated as for the IEC generator.

| IC                     | HBM-failure simulation [kV] |       | failure e | energy [µJ]       | failure<br>temperature [K] |       |  |

|------------------------|-----------------------------|-------|-----------|-------------------|----------------------------|-------|--|

|                        | reference                   | HBM/2 | reference | HBM/2<br>(factor) | reference                  | HBM/2 |  |

| μC-XC864<br>(DATA)     | 11,45                       | 5,725 | 13,27     | 4,04 (3,29)       | 1687                       | 1678  |  |

| LIN-ATA662C<br>(TXD)   | 7,0                         | 3,5   | 8,7       | 3,46 (2,52)       | 1689                       | 1682  |  |

| CAN-TJA1041T<br>(CANH) | 6,4                         | 3,2   | 24,6      | 9,6 (2,56)        | 1685                       | 1690  |  |

Table 13: Calculated factors for HBM/2 ESD robustness scaling

| IC                  | therm. capac | eitance [nJ/K] | therm. resistance [K/W] |       |  |

|---------------------|--------------|----------------|-------------------------|-------|--|

|                     | reference    | HBM/2          | reference               | HBM/2 |  |

| μC-XC864 (DATA)     | 8,87         | 2,7            | 730                     | 2400  |  |

| LIN-ATA662C (TXD)   | 5,37         | 2,13           | 470                     | 1185  |  |

| CAN-TJA1041T (CANH) | 13,9         | 5,41           | 91                      | 233   |  |

Table 14: Thermal capacitance and resistance for IC pins with HBM/2 ESD robustness

#### 3.3.3 HBM 2 kV and 1 kV robustness

The lowest critical energies are obtained with models scaled to 2 kV and 1 kV HBM charging voltage. All scaling parameters are compared in Table 15 and Table 16. The maximum scaling factor is obtained for the 2 kV HBM model of the  $\mu$ C DATA pin. Scaling factors of CAN and LIN models are similar. Critical energies remain different

for all models. The lowest critical energy is obtained in case of the  $\mu C$  scaled to 1 kV HBM level. Melting temperature is reached for a calculated energy of about 350 nJ. The active area in the semiconductor decreases so that a high thermal resistance is expected.

| 10                     |       | failure energ          | failure temperature [K] |      |      |      |

|------------------------|-------|------------------------|-------------------------|------|------|------|

| IC                     | ref.  | 2 kV<br>(factor-orig.) | 1 kV (factor-2kV)       | ref. | 2 kV | 1 kV |

| μC-XC864<br>(DATA)     | 13,27 | 0,82 (16,14)           | 0,35 (2,54)             | 1687 | 1671 | 1670 |

| LIN-ATA662C<br>(TXD)   | 8,7   | 1,66 (5,24)            | 0,69 (2,40)             | 1689 | 1675 | 1670 |

| CAN-TJA1041T<br>(CANH) | 24,6  | 5,18 (4,74)            | 2,07 (2,51)             | 1685 | 1689 | 1683 |

Table 15: Failure energies for HBM 2 kV and 1 kV scaled IC inputs

| IC                     | therm.    | capacitance | [nJ/K] | therm. resistance [K/W] |       |       |  |

|------------------------|-----------|-------------|--------|-------------------------|-------|-------|--|

| 10                     | reference | 2 kV        | 1 kV   | reference               | 2 kV  | 1 kV  |  |

| μC-XC864<br>(DATA)     | 8,87      | 0,55        | 0,23   | 730                     | 11785 | 27917 |  |

| LIN-ATA662C<br>(TxD)   | 5,37      | 1,025       | 0,42   | 470                     | 2463  | 5919  |  |

| CAN-TJA1041T<br>(CANH) | 13,9      | 2,93        | 1,17   | 91                      | 432   | 1082  |  |

Table 16: Calculated values for HBM 2 kV and 1 kV scaled IC inputs

# 3.3.4 Comparison of scaling Results

The simulated ESD robustness of all IC models is compared in terms of the critical charging voltage of IEC ESD generator and HBM generator. According to Table 17 HBM charging voltage is more than factor 2 higher than IEC charging voltage for scaled and reference models.

| IC (pin)                   | Failure Levels                    |                                   |                                   |                                   |                                   |                                   |  |

|----------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|--|

|                            | Reference model                   |                                   | 2 kV HBM                          |                                   | 1 kV HBM                          |                                   |  |

|                            |                                   |                                   | (scaled model)                    |                                   | (scaled model)                    |                                   |  |

|                            | HBM<br>failure<br>voltage<br>[kV] | IEC<br>failure<br>voltage<br>[kV] | HBM<br>failure<br>voltage<br>[kV] | IEC<br>failure<br>voltage<br>[kV] | HBM<br>failure<br>voltage<br>[kV] | IEC<br>failure<br>voltage<br>[kV] |  |

| μC-XC864<br>(DATA)         | 11,45                             | 5,5                               | 2                                 | 1,05                              | 1                                 | 0,55                              |  |

| LIN-<br>ATA662C<br>(TXD)   | 7,0                               | 3,0                               | 2                                 | 0,9                               | 1                                 | 0,5                               |  |

| CAN-<br>TJA1041T<br>(CANH) | 6,4                               | 2,5                               | 2                                 | 0,9                               | 1                                 | 0,45                              |  |

Table 17: Comparison of HBM and IEC ESD robustness of reference and scaled IC models

# 4 Measurement results

In this chapter system level measurement and simulation data are compared to verify the simulation based approach. The demonstrator PCB design is used to build up several measurement setups.

First the parameterization of the VHDL-AMS multi conductor transmission line model is verified in frequency domain. In Section 4.2 signals from IEC generator and TLP discharges are measured for two load conditions. In Section 4.3 a protection element was connected to a PCB trace (transmission line-TL). The simulated IEC robustness of the IC models is verified on the demonstrator PCB in section 4.4. The function of selected protection elements is also verified here. Results presented in section 4.5 were measured for the loop section on the demonstrator PCB.

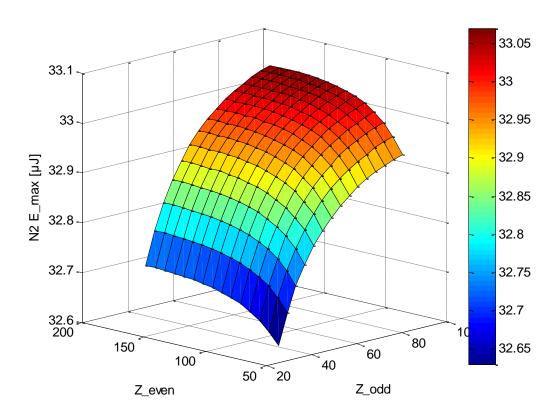

# 4.1 Coupling between striplines in frequency domain

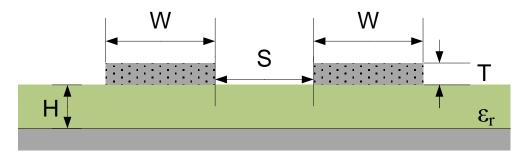

In section 2.2 the multi conductor transmission line model was verified by comparison to a highly accurate 3D simulation. The parameterization of the model has to be adapted to the structures on the demonstrator PCB. Values for common and differential mode impedances are calculated using theoretical equations for stripline configurations which are implemented in the freeware tool [16]. For the investigations a coupled multi stripline configuration over a ground plane is selected.

# 4.1.1 **Setup**

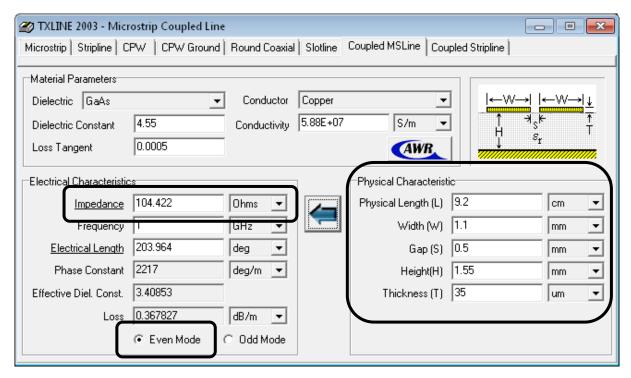

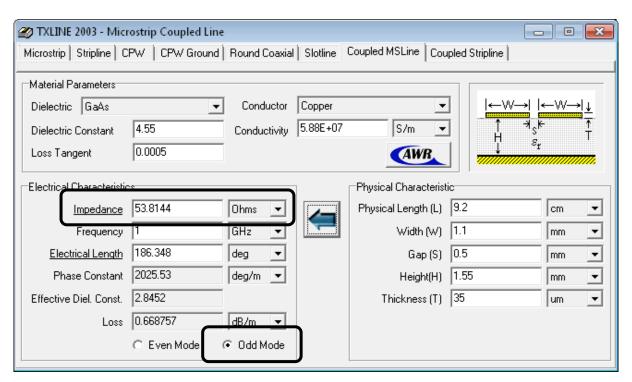

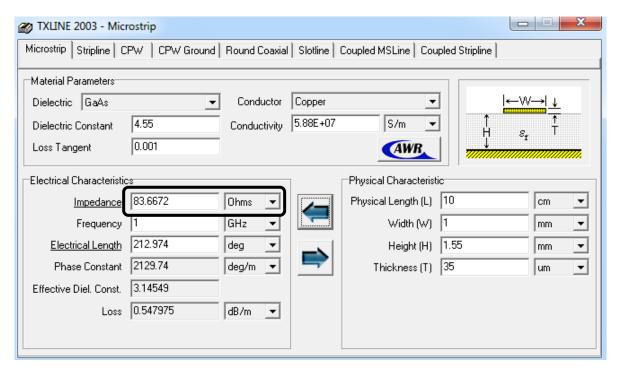

The impedances  $Z_{\text{even}}$  and  $Z_{\text{odd}}$  can be calculated with TXLINE tool for given geometry values and material parameters. It is assumed that the transmission line parameters are frequency independent. In Figure 83 and Figure 84 the parameters extracted from the PCB design presented in chapter 1 are used. The relative permittivity  $\epsilon_r$  was set to 4,55.

Figure 83: Parameter set for VHDL-AMS model in Even Mode

Figure 84: Parameter set for VHDL-AMS model in Odd Mode

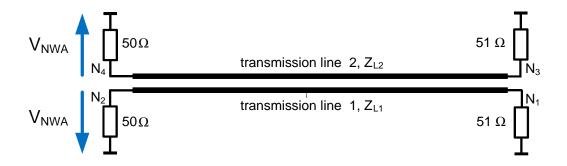

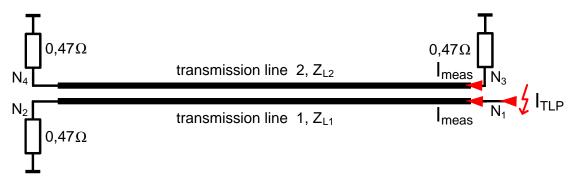

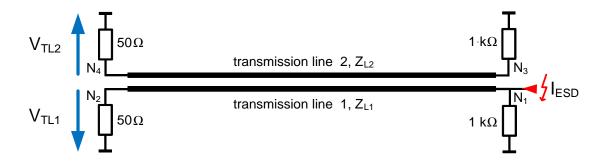

For verification of the parameter set S-parameters were measured from the crosstalk section on the demonstrator PCB with a network analyzer. A sketch of the measurement setup is shown in Figure 85. Both transmission lines are terminated with 51  $\Omega$  at nodes N3 and N1 and with the 50  $\Omega$  source impedance at nodes N2 and N4. The bandwidth was 300 kHz to 1,2 GHz.

Figure 85: Measurement setup with network analyzer

# 4.1.2 Comparison with simulation and verification of the transmission line model

The measurement setup was simulated with the calculated impedances. A transmission line length of 9,2 cm was selected. The propagation speed was not adjusted because the influence was negligible.

#### -- Parameters of MTL

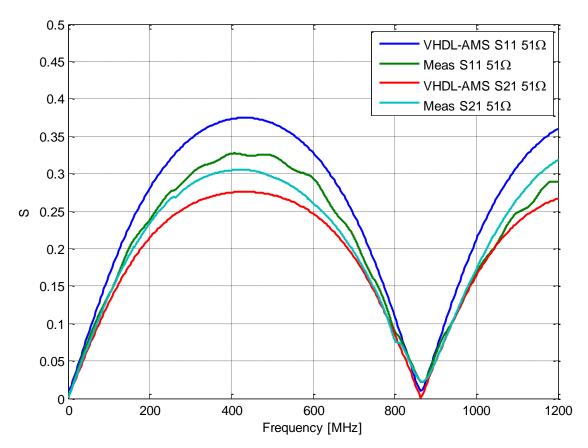

Simulation and measurement results are compared in Figure 86. Resonances of transmission and reflection S-parameters are simulated with good accuracy. Deviations of less than 10 % between the amplitudes are obtained.

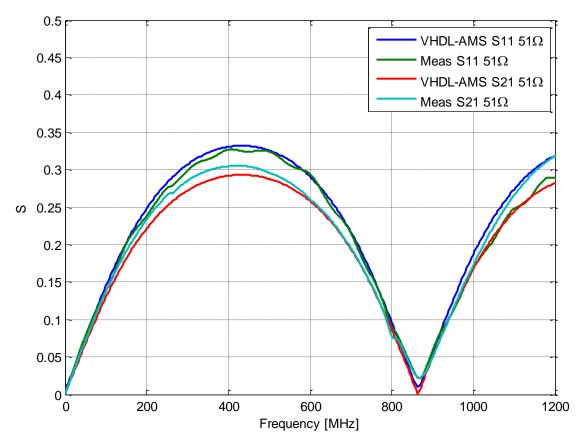

The simulation results can be improved if the gap S in the physical parameters is decreased to 0,45 mm. The impedances in the transmission line model are modified to  $Z_{\text{odd}} = 52.5059$  and  $Z_{\text{even}} = 105.219$ . In Figure 87 the measured and simulated curves are very similar with maximum deviation of about 3 %. For further investigations the original parameter set will be chosen. The influence of the differences between the parameter sets on simulation results is very low.

Figure 86: Simulation and measurement results with gap = 0,5 mm

Figure 87: Simulation and measurement results with gap = 0,45 mm

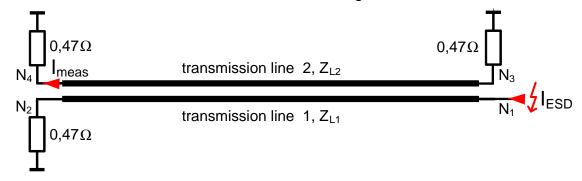

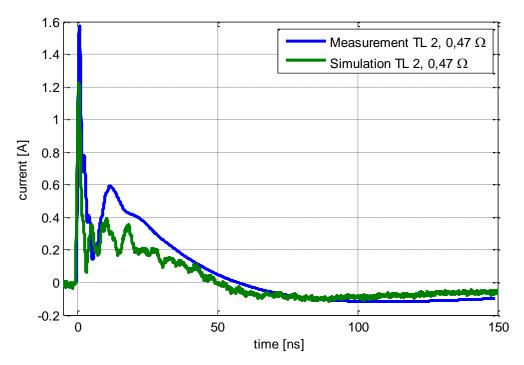

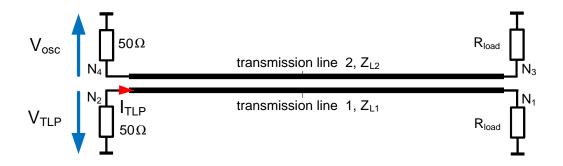

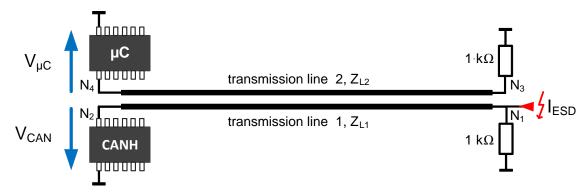

# 4.2 Measurement of cross-talk signals in time domain

In this section the simulation model of the coupled PCB trace set is verified in time domain. Two pulse generators are discharged into the PCB traces. Two configurations with low and high load resistances of the coupled traces on the cross-talk section on the demonstrator PCB are considered to cover capacitive and inductive coupling effects.

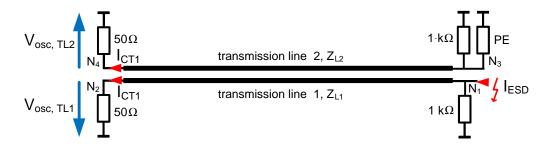

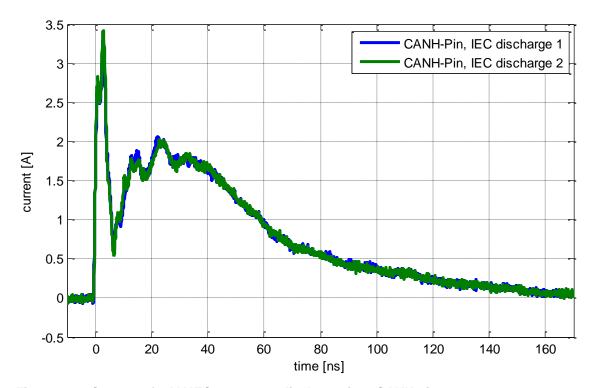

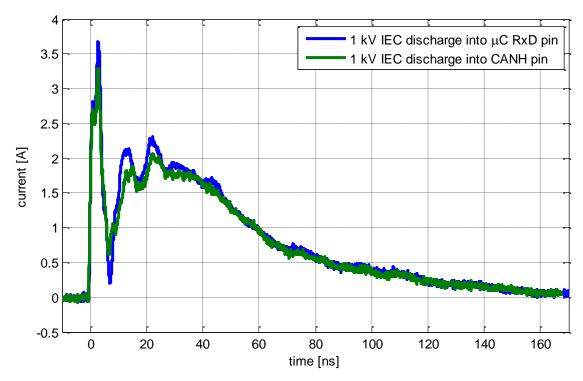

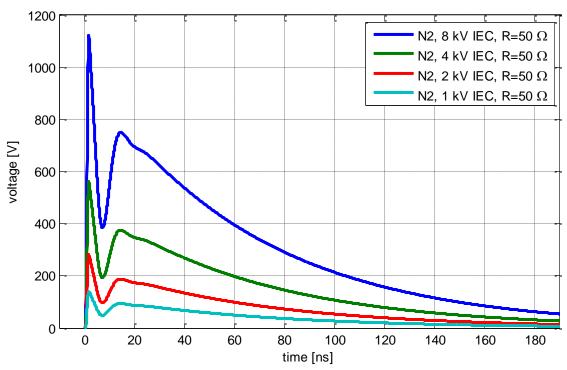

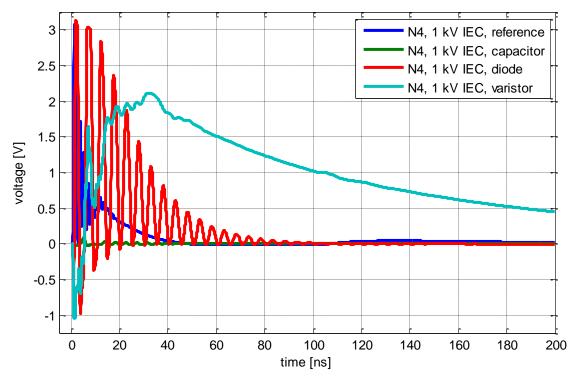

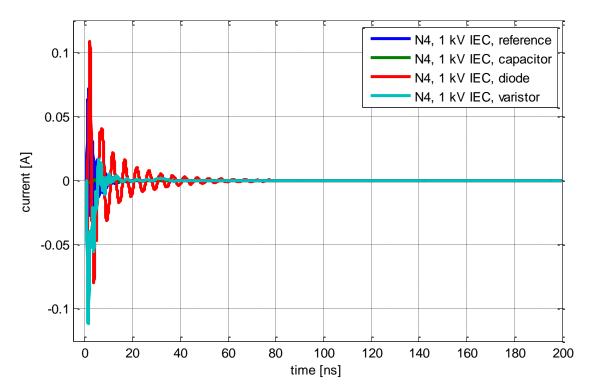

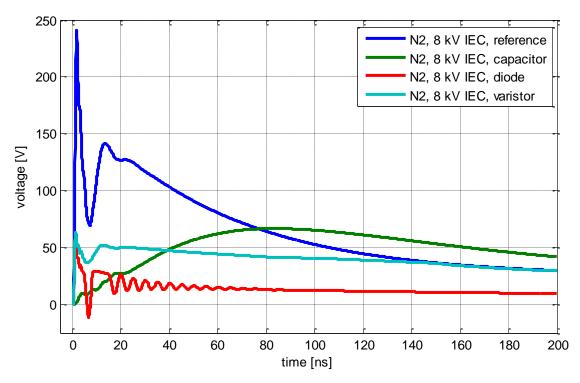

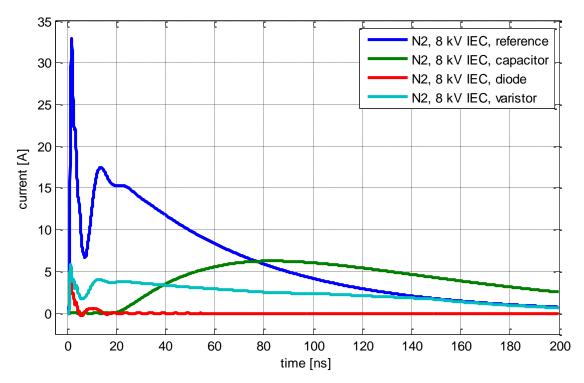

#### 4.2.1 IEC ESD Generator

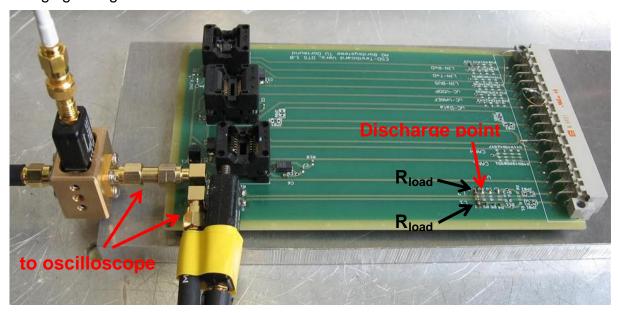

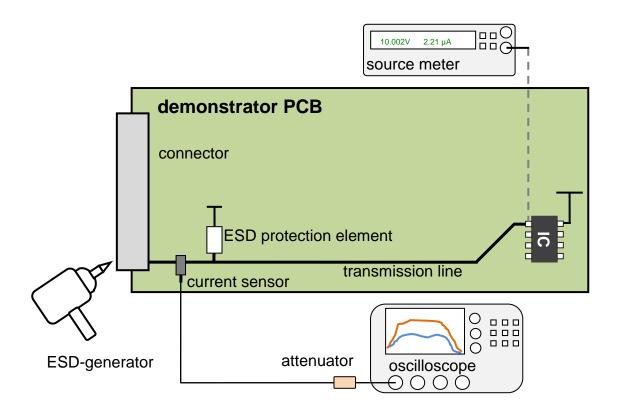

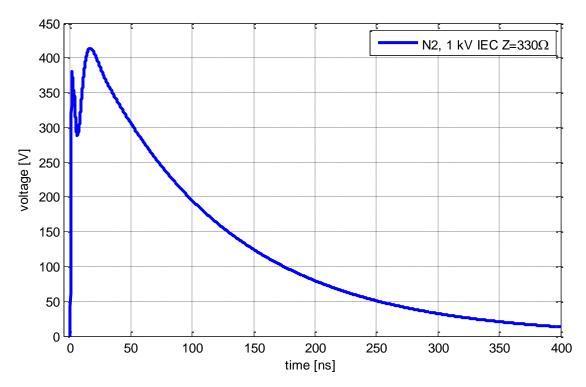

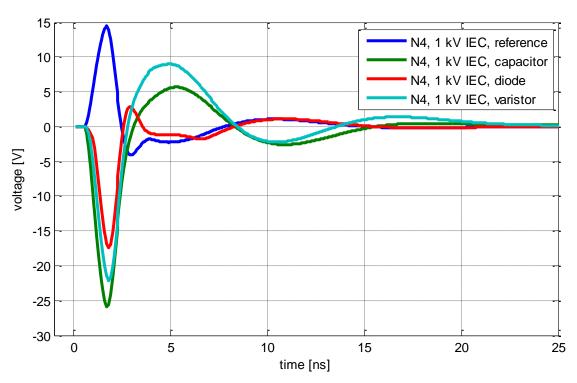

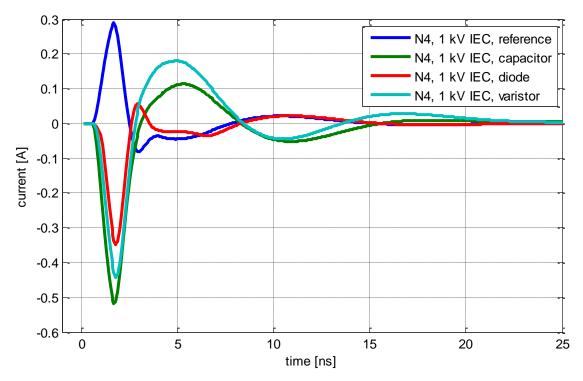

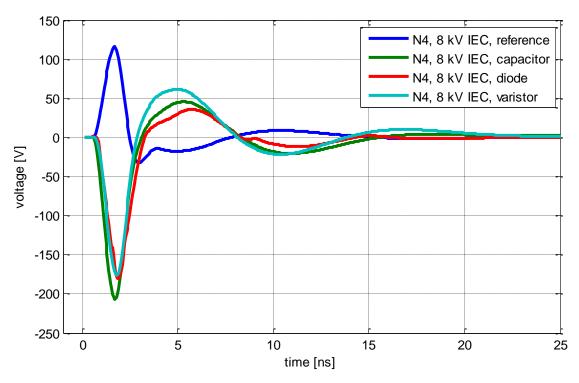

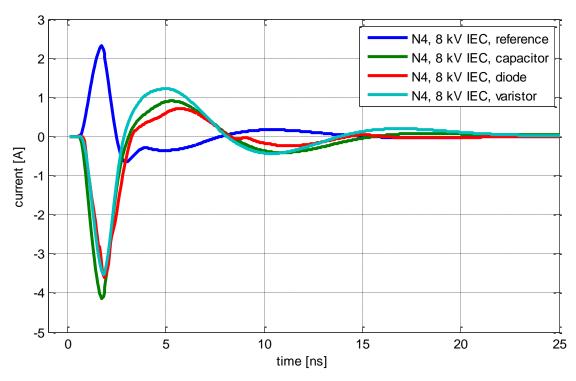

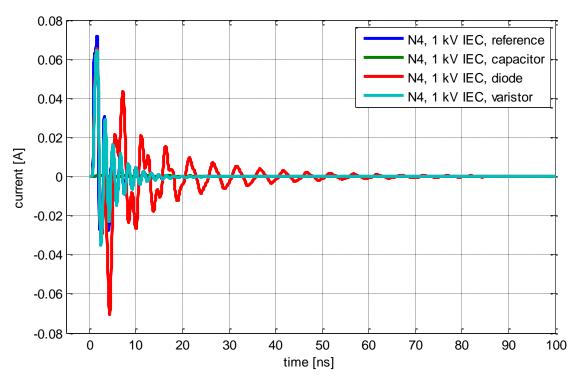

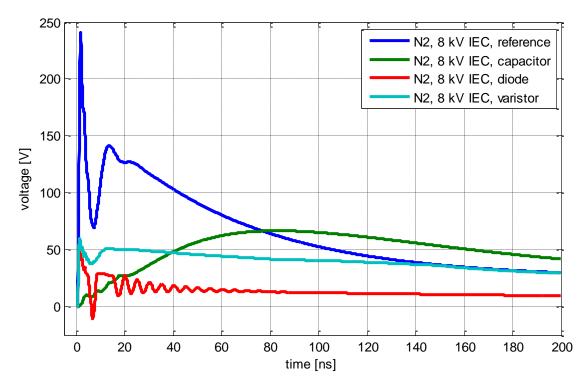

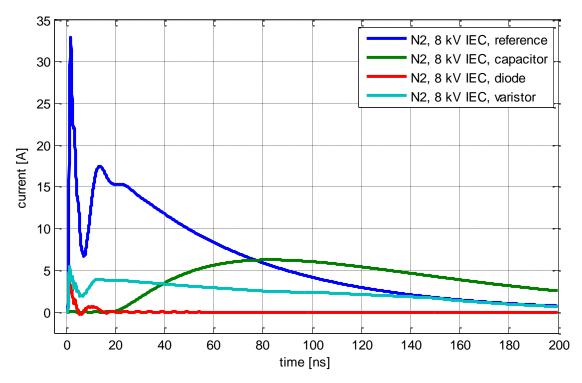

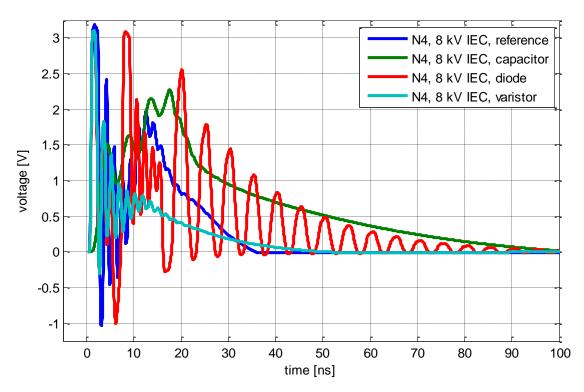

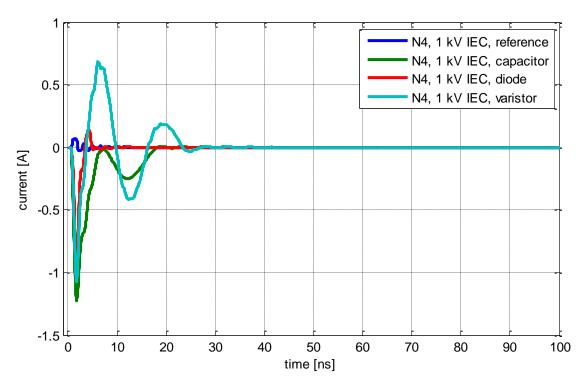

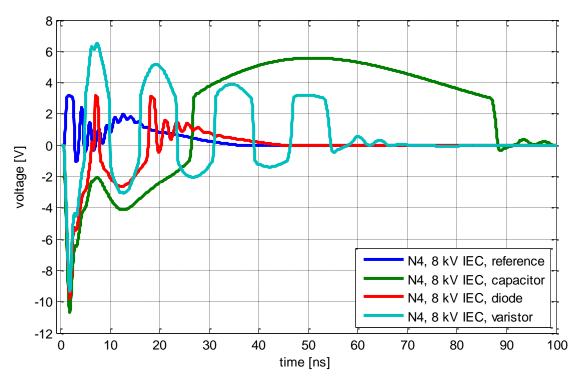

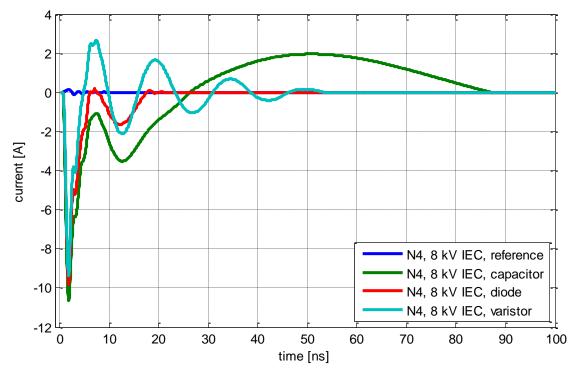

Figure 88 shows the measurement setup for the IEC generator. The current through both conductors is measured via Tektronix CT1 sensors and voltages are measured at 50  $\Omega$  instrument impedance of the oscilloscope. Both traces are terminated on the side of the discharge point with SMD devices to ground. The IEC generator is discharged via a soldering pad close to the SMD device of one transmission line. The charging voltage is set to 1 kV.

Figure 88: Measurement setup with CT1 current sensors for IEC generator discharge

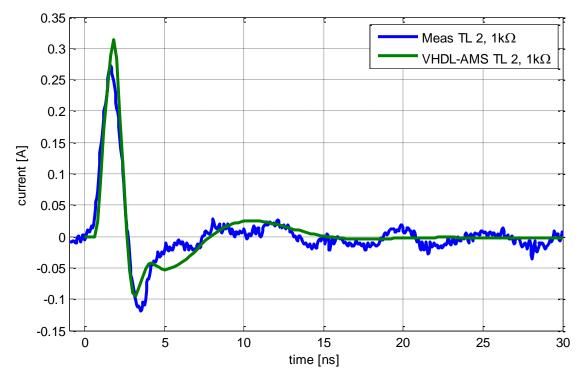

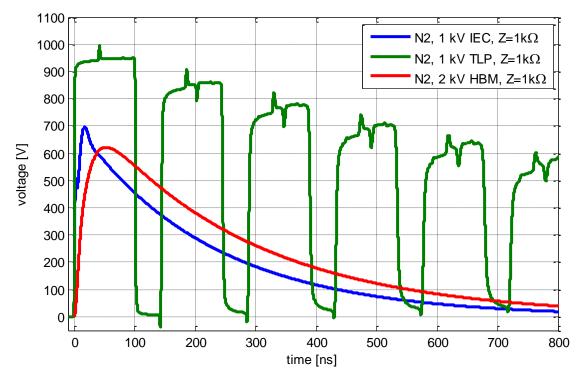

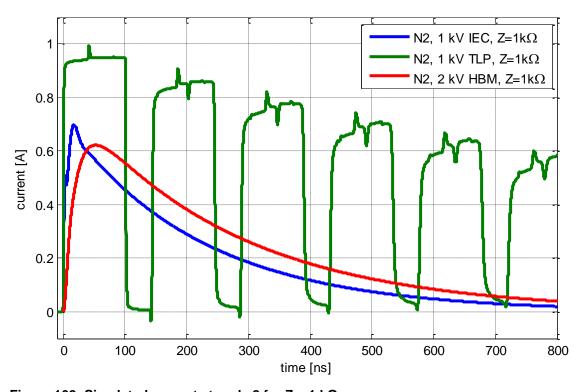

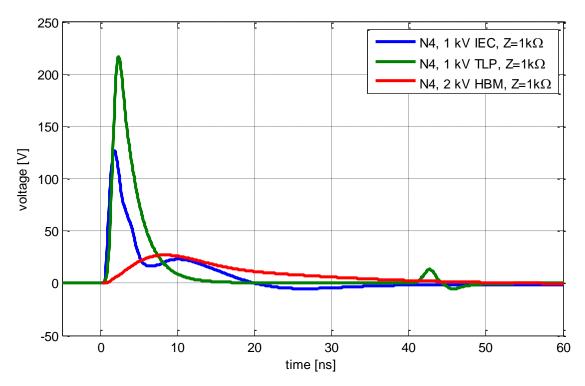

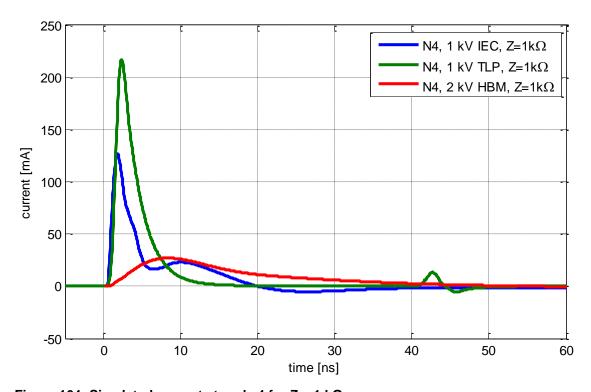

## 4.2.1.1 Measurement and simulation results for $R_{load} = 1 k\Omega$

The measurement and simulation results are presented for  $R_{load}$  = 1 k $\Omega$  at nodes N1 and N3 defined in the sketch in Figure 89.

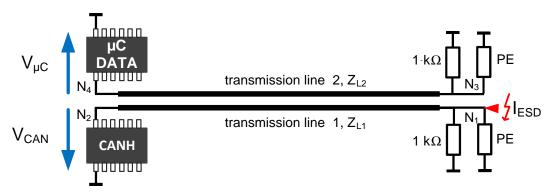

Figure 89: Measurement setup for cross-talk test with IEC generator on demonstrator PCB

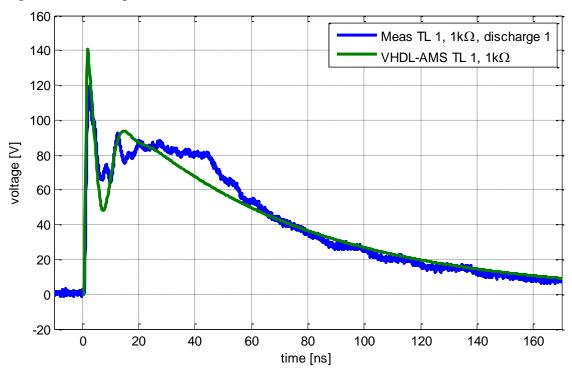

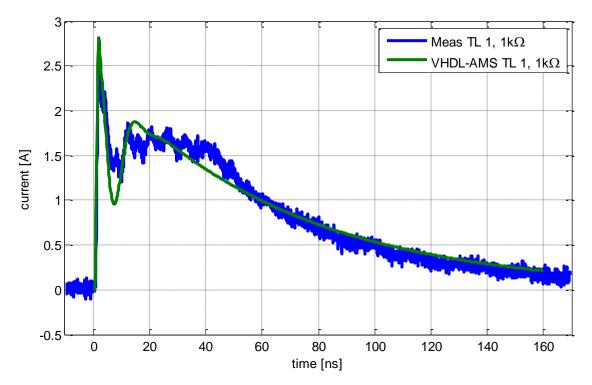

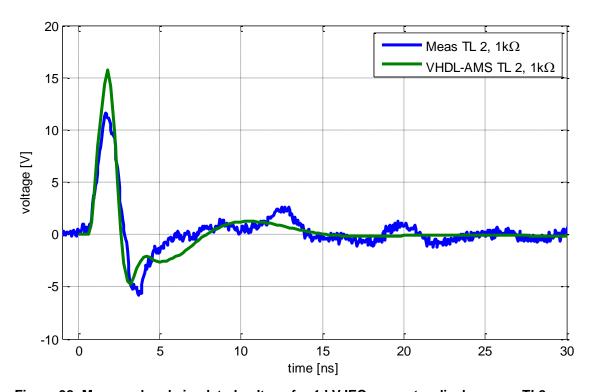

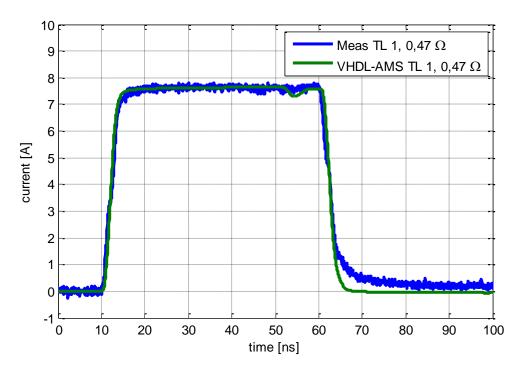

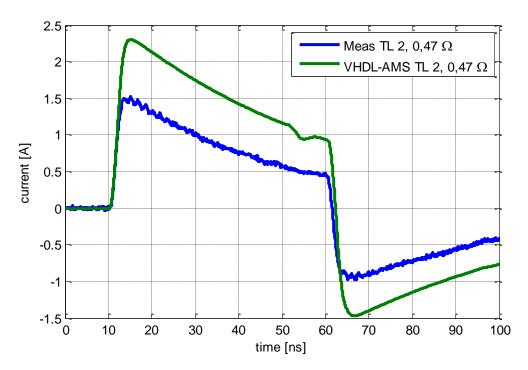

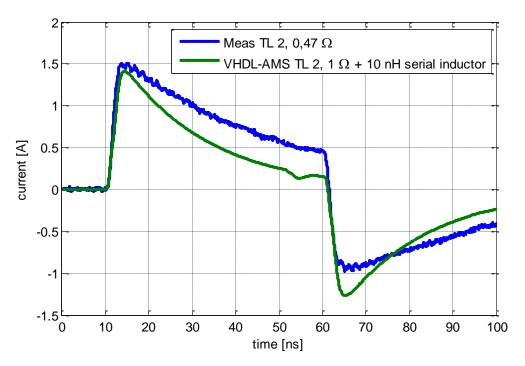

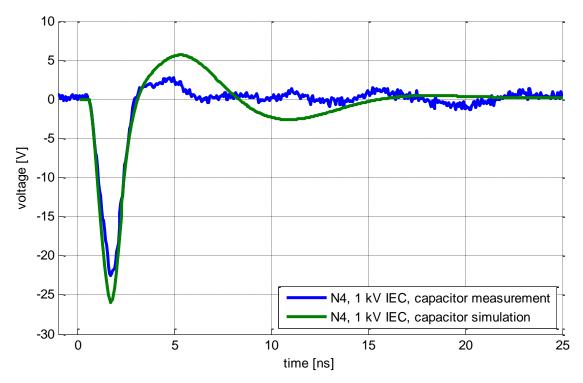

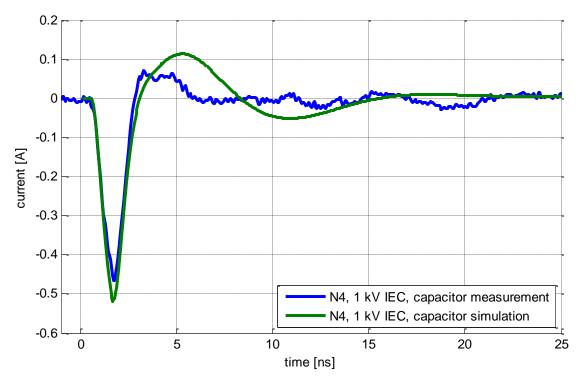

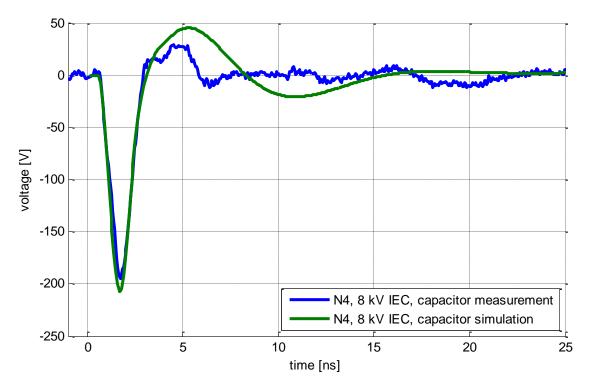

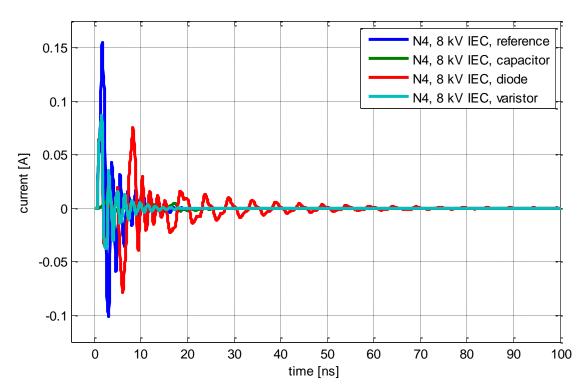

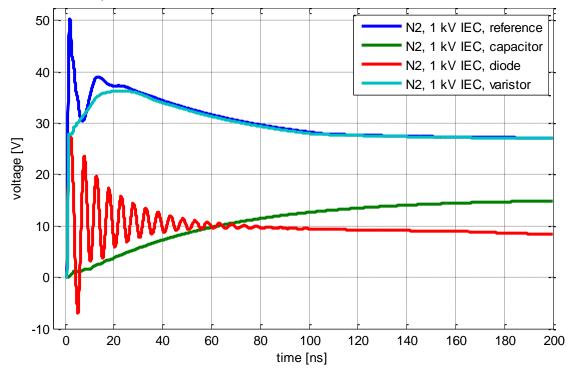

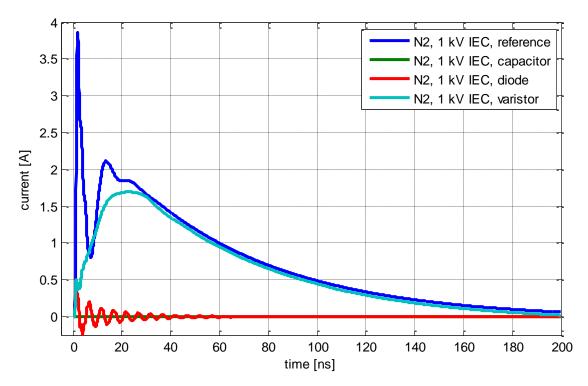

Results for voltage and current at node N2 are shown in Figure 90 and Figure 91. The simulated coupled signals at node N4 are compared to the measured shapes in Figure 92 and Figure 93.

Figure 90: Measured and simulated voltage for 1 kV IEC generator discharge on TL1

Figure 91: Measured and simulated current for 1 kV IEC generator discharge on TL1

Figure 92: Measured and simulated voltage for 1 kV IEC generator discharge on TL2

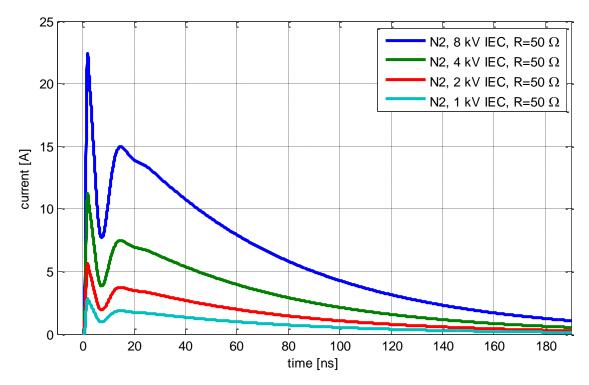

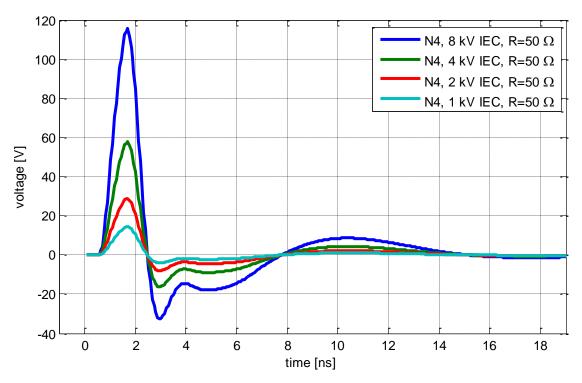

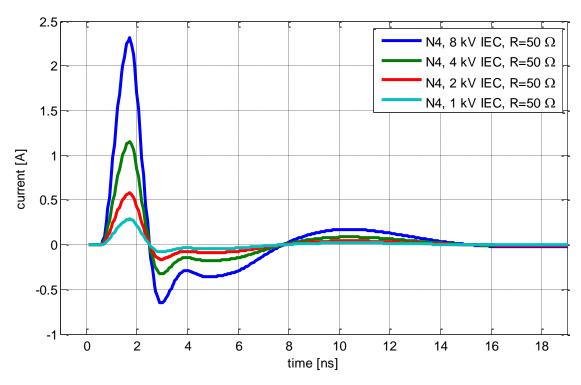

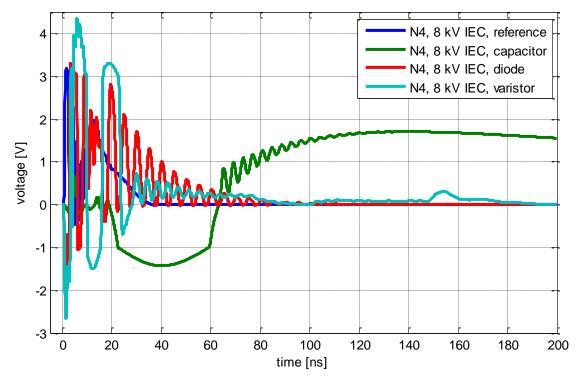

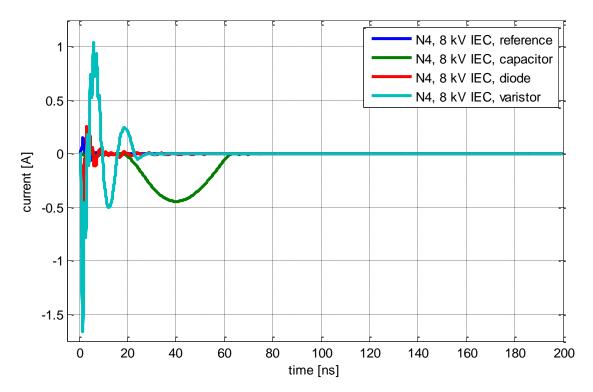

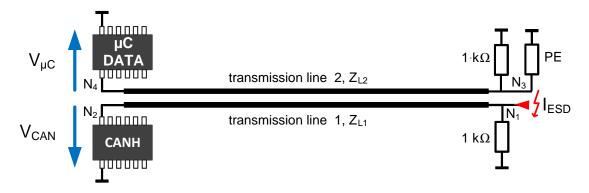

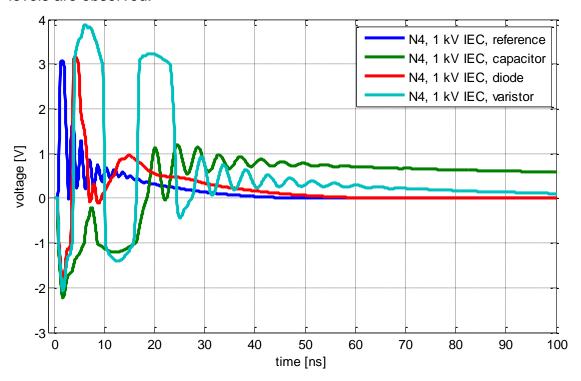

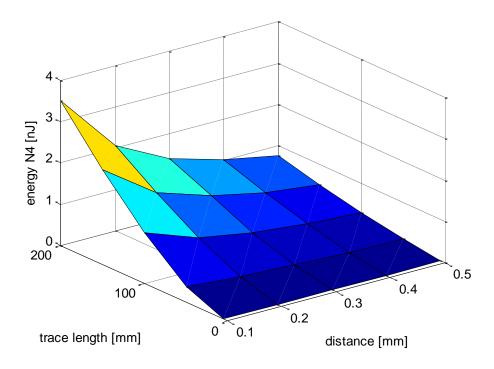

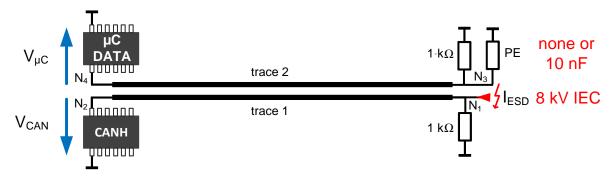

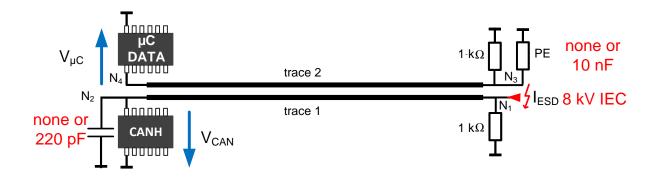

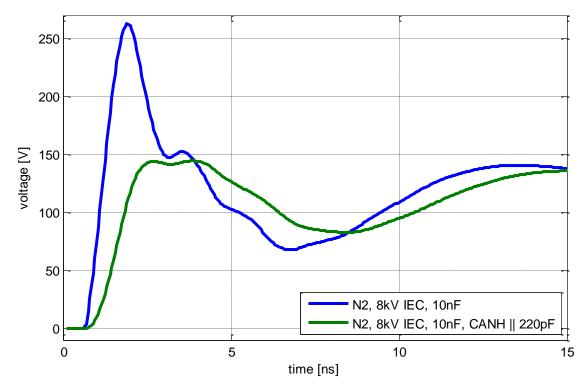

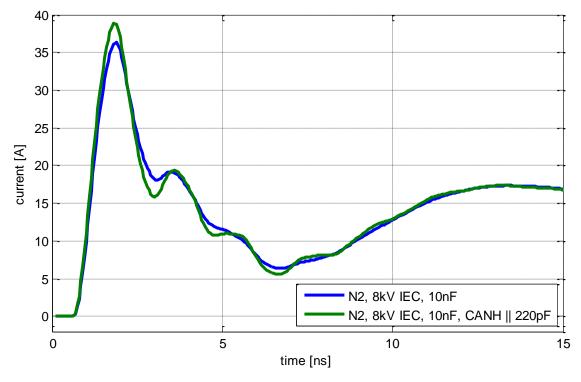

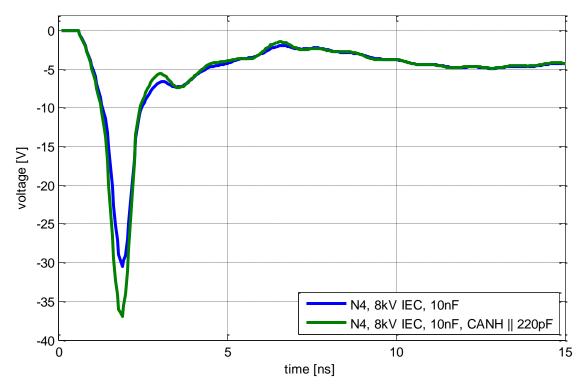

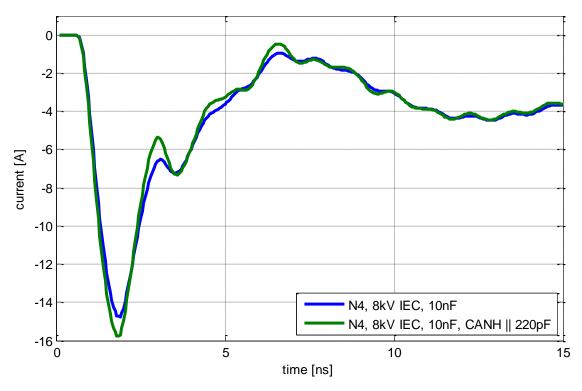

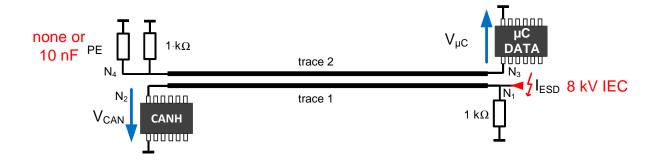

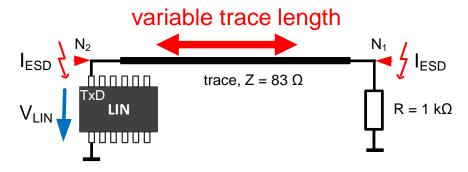

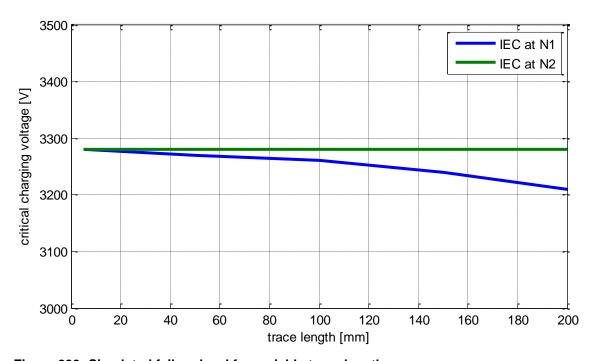

Figure 93: Measured and simulated current for 1 kV IEC generator discharge on TL2